S. BIRLA ET AL.

Copyright © 2011 SciRes. CS

327

maintain their states is the bit-cell’s SNM. The SNM is

the maximum amount of noise voltage that can be intro-

duced at the output of the two inverters, such that the cell

retains its data. SNM quantifies the amount of noise vol-

tage required at the internal nod es of a bit-cell to flip th e

cell’s contents [2]. The static noise margin is a measure

of the cell’s ability to retain its data state. The worst-case

situation is usually under “read-disturb” condition [3].

When the word-line device is turned on and connects the

pre-charged bit-line to the low side of the cell. The state

of the cell may flip if the internal node voltage rises to a

high enough level. The problem is exacerbated if the

ratio of the conductance of the pull-down and the word-

line devices (often called beta) is too small.

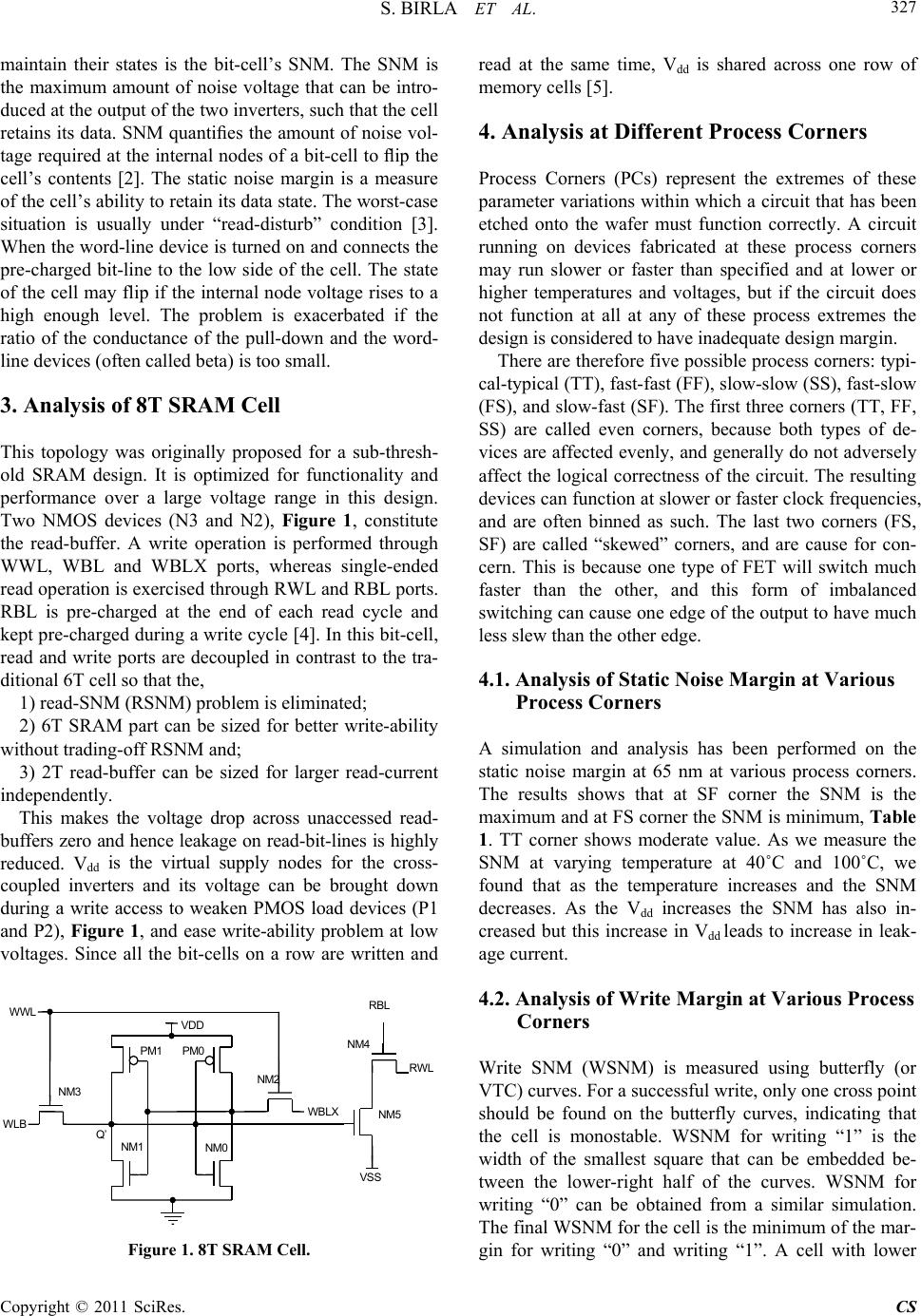

3. Analysis of 8T SRAM Cell

This topology was originally proposed for a sub-thresh-

old SRAM design. It is optimized for functionality and

performance over a large voltage range in this design.

Two NMOS devices (N3 and N2), Figure 1, constitute

the read-buffer. A write operation is performed through

WWL, WBL and WBLX ports, whereas single-ended

read operation is exercised through RWL and RBL ports.

RBL is pre-charged at the end of each read cycle and

kept pre-charged during a write cycle [4]. In th is bit-cell,

read and write ports are decoupled in contrast to the tra-

ditional 6T cell so that the,

1) read-SNM (RSNM) problem is eliminated;

2) 6T SRAM part can be sized for better write-ability

without trading-off RSNM and;

3) 2T read-buffer can be sized for larger read-current

independently.

This makes the voltage drop across unaccessed read-

buffers zero and hence leakage on read-bit-lines is highly

reduced. Vdd is the virtual supply nodes for the cross-

coupled inverters and its voltage can be brought down

during a write access to weaken PMOS load devices (P1

and P2), Figure 1, and ease write-ability problem at low

voltages. Since all the bit-cells on a row are written and

NM2

VDD

WWL

PM1 PM0

NM1

WLB

NM3

WBLX

NM0

Q’

VSS

RBL

RWL

NM4

NM5

Figure 1. 8T SRAM Cell.

read at the same time, Vdd is shared across one row of

memory cells [5].

4. Analysis at Different Process Corners

Process Corners (PCs) represent the extremes of these

parameter variations within which a circuit that has been

etched onto the wafer must function correctly. A circuit

running on devices fabricated at these process corners

may run slower or faster than specified and at lower or

higher temperatures and voltages, but if the circuit does

not function at all at any of these process extremes the

design is considered to have inadequate design margin.

There are therefore five possible process corners: typi-

cal-typical (TT), fast-fast (FF), slow-slow (SS), fast-slow

(FS), and slow-fast (SF). The first three corners (TT, FF,

SS) are called even corners, because both types of de-

vices are affected evenly, and generally do not adversely

affect the logical correctness of the circuit. The resulting

devices can function at slower or faster clock frequencies,

and are often binned as such. The last two corners (FS,

SF) are called “skewed” corners, and are cause for con-

cern. This is because one type of FET will switch much

faster than the other, and this form of imbalanced

switching can cause one edge of the output to have much

less slew than the other edge.

4.1. Analysis of Static Noise Margin at Various

Process Corners

A simulation and analysis has been performed on the

static noise margin at 65 nm at various process corners.

The results shows that at SF corner the SNM is the

max imu m and a t FS co rn er the S NM is mini mum, Table

1. TT corner shows moderate value. As we measure the

SNM at varying temperature at 40˚C and 100˚C, we

found that as the temperature increases and the SNM

decreases. As the Vdd increases the SNM has also in-

creased but this increase in Vdd leads to increase in leak-

age current.

4.2. Analysis of Write Margin at Various Process

Corners

Write SNM (WSNM) is measured using butterfly (or

VTC) curves. For a successful write, only one cross point

should be found on the butterfly curves, indicating that

the cell is monostable. WSNM for writing “1” is the

width of the smallest square that can be embedded be-

tween the lower-right half of the curves. WSNM for

writing “0” can be obtained from a similar simulation.

The final WSNM for the cell is the minimum of the mar-

gin for writing “0” and writing “1”. A cell with lower