International Journal of Communications, Network and System Sciences

Vol.09 No.11(2016), Article ID:72222,10 pages

10.4236/ijcns.2016.911042

Fixed Point Iteration Chaos Controlled ZCDPLL

Qassim Nasir

Electrical and Computer Engineering Department, University of Sharjah, Sharjah, UAE

Copyright © 2016 by author and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Received: September 26, 2016; Accepted: November 21, 2016; Published: November 24, 2016

ABSTRACT

The stable operation of first and second order Zero Crossing Digital Phase Locked Loop (ZCDPLL) is extended by using a Fixed Point Iteration (FPI) method with relaxation. The non-linear components of ZCDPLL such as sampler phase detector and Digital Controlled Oscillator (DCO) lead to unstable and chaotic operation when the filter gains are high. FPI will be used to stabilize the chaotic operation and consequently extend the lock range of the loop. The proposed stabilized loop can work in higher filter gains which are needed for faster signal acquisition.

Keywords:

Non-Uniform Sampling, Digital Phase Locked Loops, Zero Crossing DPLL, Chaos Control

1. Introduction

Digital Phase Locked Loop (PLL) has been widely used and for many years in wireless and wired communications subsystems. It is an essential component in clock and carrier recovery, and frequency synthesizer. Digital Phase locked Loops (DPLLs) have better reliability and higher stability compared to analogue counterpart at lower cost and can easily be part of a digital processing equipment [1] . The researchers show strong interest in the design of digital PLLs (DPLLs) to solve problems associated with analog DPLLS, such as, sensitivity to DC drift and component inaccuracies and saturation, and their need for initial calibration [1] [2] . The sampler type classifies DPLL into two major categories: uniform sampling DPLLs (US-DPLLs) and non-uniform sampling DPLLs (NUS-DPLLs). Different types of NUS-DPLLs have been introduced according to the way to detect the phase difference between locally generated carrier and the input signal to the loop from the sampled signal such as zero crossing DPLL (ZCDPLL) [3] [4] and digital tan-lock loop (DTLL) [5] [6] [7] . ZCDPLL is a closed loop system used to follow the zero crossing of the input carrier signal. It consists of a sampler (acting as a phase detector), a digital loop filter and a digital controlled oscillator [8] [9] [10] [11] . The most commonly used DPLL is the Zero Crossing Digital Phase Locked Loop (ZCDPLL). The operation is based on tracking the signal input phase by using non uniform sampling techniques. The sample value is a function of the signal input phase. These values are filtered before they are used back to control the next sampling time by the help of Digital Controlled Oscillator (DCO). The non-linear behaviour of ZCDPLL leads bifurcation instabilities to its path to chaos [12] .

A number of methods were proposed for chaos control [13] such as using Pyragas method to broaden the tracking range by extending the stable operation behaviour of ZCDPLL to a larger digital filter gain, which leads to larger input frequency [11] . Fixed Point Iteration (FPI) with relaxation will be presented to extend the stable operation range of both first and second order ZCDPLL. The stabilized loops are analyzed and the results are verified using bifurcation theory and a numerical simulation. It is the first time that FPI used to stabilize the chaotic operation of the DPLL.

In Section 2, the conventional first order ZCDPLL operation is described. Section 3 discusses the Fixed Point stabilization algorithm, and in section 4 the second order ZCDPLL is presented, while Section 5 details the operation of the second order ZCDPLL when FPI chaos control is included in the loop. Simulation results are presented in Section 6 and finally conclusions are given in Section 7.

2. First Order ZCDPLL

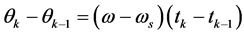

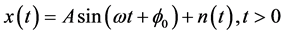

Conventional first order ZCDPLL is shown in Figure 1. Let us assume that the input signal  is defined as

is defined as

(1)

(1)

where  is Additive White Gaussian Noise (AWGN),

is Additive White Gaussian Noise (AWGN),  is initial phase (can be assume zero without loosing generality),

is initial phase (can be assume zero without loosing generality),  is the input signal frequency, and

is the input signal frequency, and  is the nominal frequency or DCO free running frequency when no input signal is applied. The input signal is assumed to be noise free [

is the nominal frequency or DCO free running frequency when no input signal is applied. The input signal is assumed to be noise free [ ]. This input signal

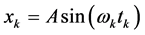

]. This input signal  is sampled at

is sampled at  instants determined by DCO.

instants determined by DCO.

(2)

(2)

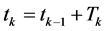

the sampling instants  can be represented by

can be represented by

Figure 1. Block diagram of conventional first ZCDPLL.

(3)

(3)

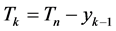

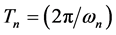

is the Digital Controlled Oscillator (DCO) period, which is given by [15] :

is the Digital Controlled Oscillator (DCO) period, which is given by [15] :

(4)

(4)

where  is the nominal period,

is the nominal period,  is the output of digital filter. The input signal phase can be represented as

is the output of digital filter. The input signal phase can be represented as

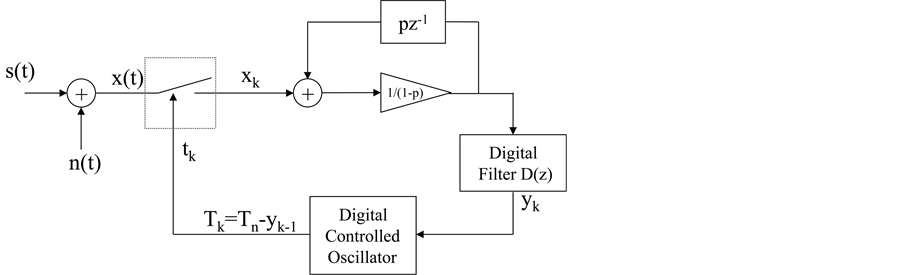

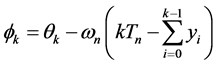

The phase error

Then

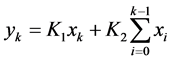

The sampled values

where K is the zero order filter gain (First Order ZCDPLL), while for first order filter or second order ZCDPLL, the outputs will be:

where

where

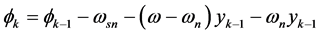

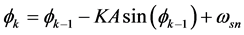

Therefore first order ZCDPLL phase error operation function will be:

The phase error mapping function (

3. Extending the Stable Operation of First Order ZCDPLL

Various methods and techniques were used to control the instability of chaotic operation of control loop such as Ott-Grebogi-Yorke (OGY) or Pyragas [14] . In this paper the Fixed Point Iteration (FPI) with relaxation is used to extend the stable operation of the ZCDPLL. FPI was used the first time by Babylonian (2000 B.C) to estimate the square root. The original version was used for finding

Then Hillam [16] proposed FPI with relaxation for fixed point stability as follow:

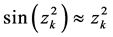

p is fractional constant which control the amount of feedback. This algorithm can’t be used when

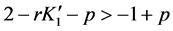

The system will be stable when

where

The stabilized first order ZCDPLL using FPI with relaxation is shown in Figure 2.

4. Second Order ZCDPLL Operation

The first order filter transfer function

Figure 2. FPI chaos controlled first order ZCDPLL.

Then

To express Equation (16) in time domain:

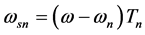

Then the operation Equations (10) is given by [17]

If we assume

To guarantee the stable operation of the loop, then inequality should be satisfied [17]

5. Extending the Stable Operation of Second Order ZCDPLL

The proposed FPI with relaxation for fixed point stability is applied for second order as well and the new operation equation can be written as:

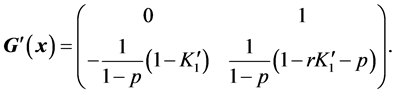

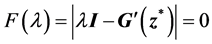

The system state vector is defined as

around the stable operating point

In order to have eigen values of

Using Jury stability test [18] , the roots of the polynomial

Since

plied on

6. System Performance

The first and second order conventional and FPI chaos controlled ZCDPLL is simulated by using MATLAB. The input signal is assumed to be

quency of DCO is

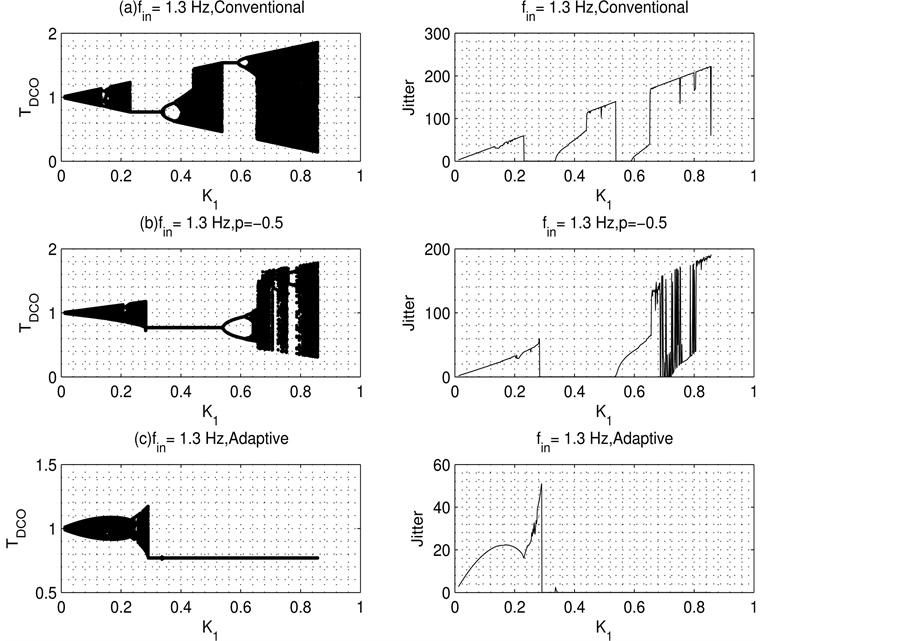

First order ZCDPLL is subjected to a frequency step of 1.3 Hz. Then

=

controlled first order ZCDPLL bifurcates

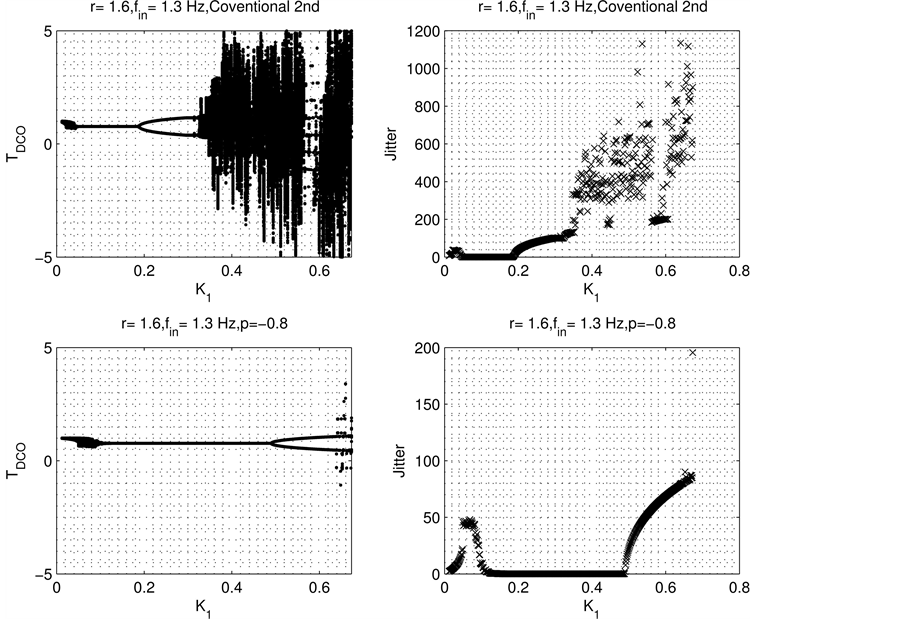

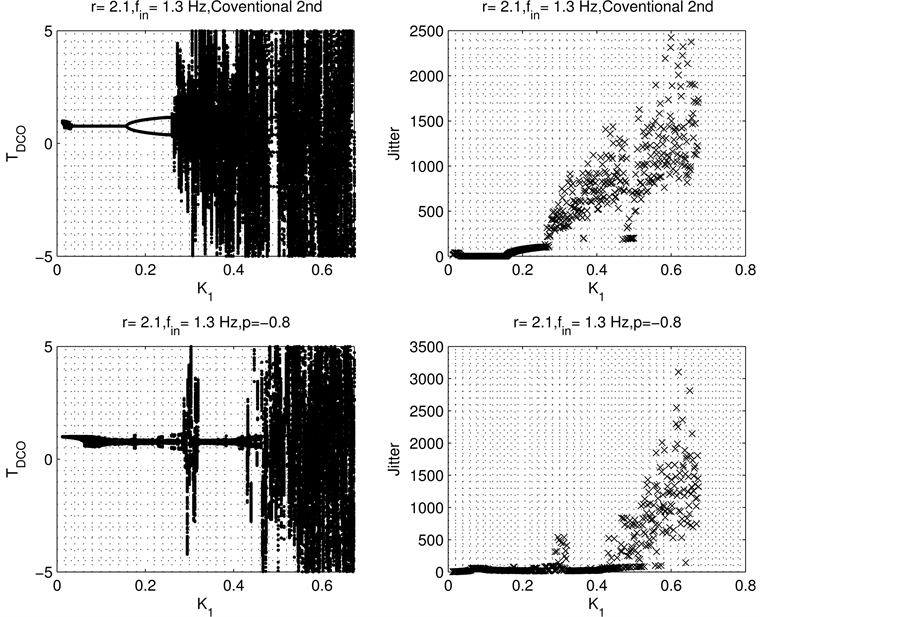

There are two filter parameters in the second order loop (

that the FPI chaos controlled loop has extended stable operation when the filter parameter (

Figure 3. First order FPI-ZCDPLL performance for different values of p.

Figure 4. Second order FPI-ZCDPLL performance for different values of p and

Figure 5. Second order FPI-ZCDPLL performance for different values of p and

Figure 6. Second order FPI-ZCDPLL performance for different values of p and

7. Conclusion

This paper proposes a Fixed Point Iteration (FPI) with relaxation to control the chaotic operation of the ZCDPLL. The analytic expressions for the stable operation for both conventional and FPI chaos control first and second order ZCPLL are found and confirmed by simulation. It is found that the lock range of the FPI chaos controlled loop is larger than that of the conventional loop for both orders. The validity of the results is conformed through numerical simulations. It is also found that careful selection of chaos control parameters is needed to ensure that the loop is still working in stable operation. This extended operation of the ZCDPLL leads to larger lock range. The larger values of filter gains of FPI chaos controlled will automatically decrease the input signal acquisition time.

Cite this paper

Nasir, Q. (2016) Fixed Point Iteration Chaos Controlled ZCDPLL. Int. J. Communications, Network and System Sciences, 9, 535-544. http://dx.doi.org/10.4236/ijcns.2016.911042

References

- 1. Lindsay, W. and Chie, C.M. (1981) A Survey of Digital Phase Locked Loops. IEEE Proceeding, 69, 410-431.

http://dx.doi.org/10.1109/PROC.1981.11986 - 2. Al-Araji, S.R., Hussain, Z.M. and Al-Qutayri, M.A. (2006) Digital Phase Lock Loops: Architectures and Applications. Kluwer Academic Publishers (Springer), Netherlands.

http://dx.doi.org/10.1007/978-0-387-32864-5 - 3. Nasir, Q. (2015) FIR Digital Filter Based ZCDPLL for Carrier Recovery. International Journal of Electronics, 103, 736-746.

http://dx.doi.org/10.1080/00207217.2015.1046501 - 4. Nasir, Q. and Al-Araji, S. (2011) Linearized Phase Detector Zero Crossing DPLL Performance Evaluation in Faded Mobile Channels. Circuits and Systems, 2, 139-144.

http://dx.doi.org/10.4236/cs.2011.23021 - 5. Lee, J. and Un, C. (1982) Performance Analysis of Digital Tanlock Loop. IEEE Transactions on Communications, 30, 2398-2411.

http://dx.doi.org/10.1109/TCOM.1982.1095407 - 6. Hussain, Z.M. and Boashash, B. (2002) The Time-Delay Digital Tanlock Loop: Performance Analysis in Additive Gaussian Noise. Journal of the Franklin Institute, 339, 4360.

http://dx.doi.org/10.1016/S0016-0032(01)00059-X - 7. Sarkar, B.C., De Sarkar, S.S. and Banerjee, T. (2014) Nonlinear Dynamics of a Class of Digital Tan-Lock Loops with Non-Ideal Phase Detector. Signal Processing, 104, 311-318.

http://dx.doi.org/10.1016/j.sigpro.2014.04.008 - 8. Nasir, Q. and Al-Araji, S. (2009) Performance Analysis of Zero Crossing DPLL with Linearized Phase Detector. International Journal of Information and Communication Technology, 1.

- 9. Al-Araji, S., Mezher, K. and Nasir, Q. (2013) First-Order Digital Phase Lock Loop with Continuous Locking. 5th International Conference on Computational Intelligence, Communication Systems and Networks, Madrid, 5-7 June 2013, 414-417.

http://dx.doi.org/10.1109/cicsyn.2013.30 - 10. Nasir, Q. and Al-Araji, S. (2013) Performance Evaluation of Sigma Delta Zero Crossing DPLL. The IEEE International Conference on Electronics, Circuits, and Systems, 11-14 December 2011, Beirut.

- 11. Nasir, Q. (2005) Extended Lock Range Zero-Crossing Digital Phase-Locked Loop with Time Delay. EURASIP Journal on Wireless Communications and Networking EURASIP JWCN, 3, 413-418.

http://dx.doi.org/10.1155/wcn.2005.413 - 12. Nasir, Q. (2004) Chaotic Behaviour of First Order Zero Crossing Digital Phase Locked Loop. IEEE Asia-Pacific Conference on Circuits and Systems, 977-980.

http://dx.doi.org/10.1109/apccas.2004.1413044 - 13. Fradkov, A.L. and Evans, R.E. (2002) Control of Chaos: Survey 1997-2000. Proceedings of 15th IFAC World Congress, Barcelona.

http://dx.doi.org/10.3182/20020721-6-es-1901.01645 - 14. Pyragas, K. (1992) Continuous Control of Chaos by Self-Controlling Feedback. Physical Letters A, 170, 412-428.

http://dx.doi.org/10.1016/0375-9601(92)90745-8 - 15. Osborne, H.C. (1980) Stability Analysis of an Nth Power Phase-Locked Loop-Part I: First Order DPLL. IEEE Transactions on Communications, 28, 1343-1354.

http://dx.doi.org/10.1109/TCOM.1980.1094771 - 16. Hillam, B. (1975) A Generalization of Kransnoselki’s Theorem on the Real Line. Mathematics Magazine, 48, 167-168.

http://dx.doi.org/10.2307/2689700 - 17. Osborne, H.C. (1980) Stability Analysis of an Nth Power Phase-Locked Loop-Part II: Second- and Third-Order DPLLs. IEEE Transactions on Communications, 28, 1355-1364.

http://dx.doi.org/10.1109/TCOM.1980.1094772 - 18. Kuo, B.C. (1963) Analysis and Synthesis of Sampled Data Control Systems. Prentice Hall, Englewood Cliffs.