S. BIRLA ET AL.

276

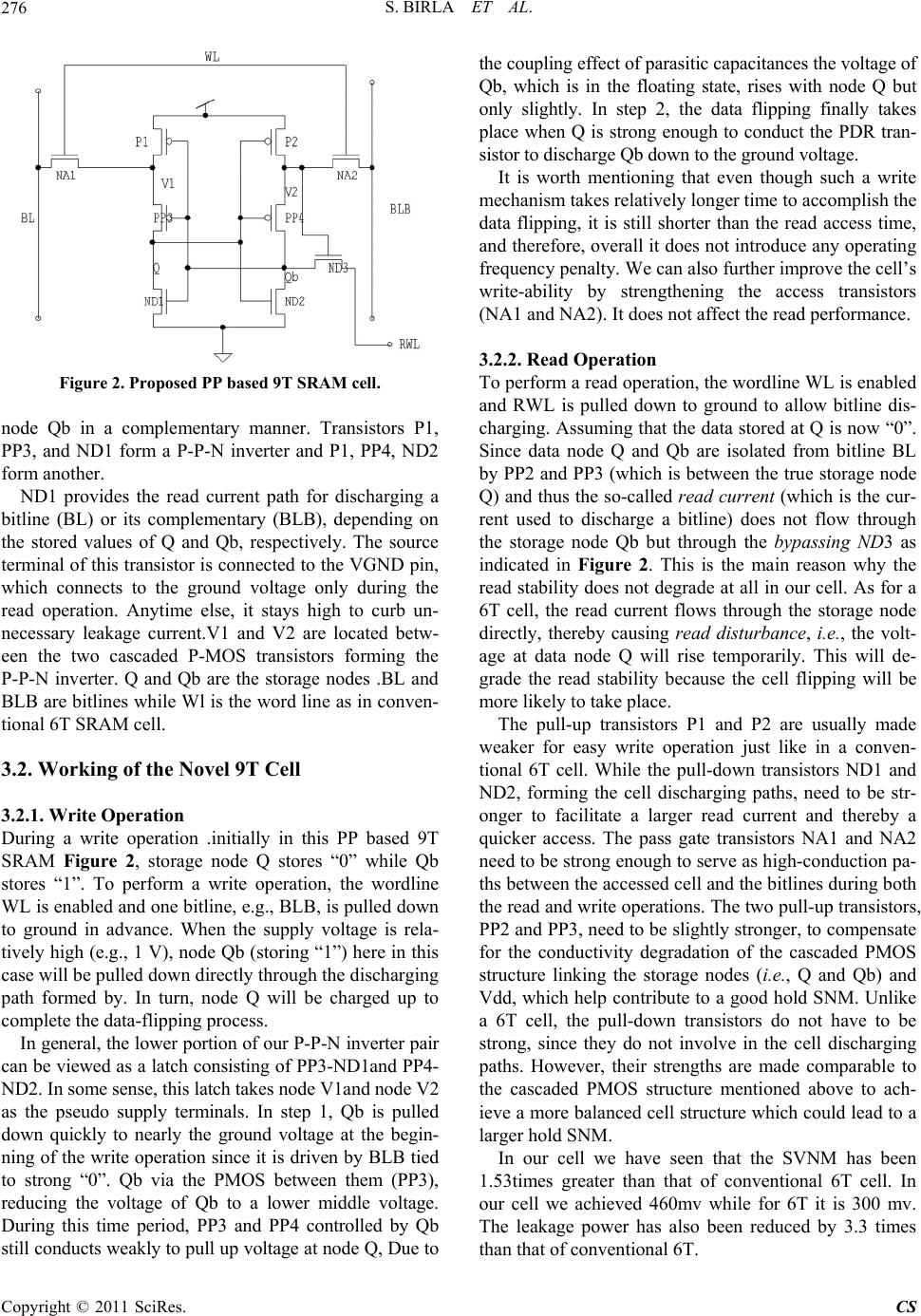

Figure 2. Proposed PP based 9T SRAM cell.

node Qb in a complementary manner. Transistors P1,

PP3, and ND1 form a P-P-N inverter and P1, PP4, ND2

form another.

ND1 provides the read current path for discharging a

bitline (BL) or its complementary (BLB), depending on

the stored values of Q and Qb, respectively. The source

terminal of this transistor is connected to the VGND p in,

which connects to the ground voltage only during the

read operation. Anytime else, it stays high to curb un-

necessary leakage current.V1 and V2 are located betw-

een the two cascaded P-MOS transistors forming the

P-P-N inverter. Q and Qb are the storage nodes .BL and

BLB are bitlines while Wl is the word line as in conv en-

tional 6T SRAM cell.

3.2. Working of the Novel 9T Cell

3.2.1. Write Operation

During a write operation .initially in this PP based 9T

SRAM Figure 2, storage node Q stores “0” while Qb

stores “1”. To perform a write operation, the wordline

WL is enabled and one bitline, e.g., BLB, is pu lled down

to ground in advance. When the supply voltage is rela-

tively high (e.g., 1 V) , node Qb (storing “1”) here in this

case will be pulled down directly through the discharg ing

path formed by. In turn, node Q will be charged up to

complete the data-flipping process.

In general, the lower portion of our P-P-N inverter pair

can be viewed as a latch consisting of PP3-ND1and PP4-

ND2. In some sense, this latch takes node V1and node V2

as the pseudo supply terminals. In step 1, Qb is pulled

down quickly to nearly the ground voltage at the begin-

ning of the write operation since it is driven by BLB tied

to strong “0”. Qb via the PMOS between them (PP3),

reducing the voltage of Qb to a lower middle voltage.

During this time period, PP3 and PP4 controlled by Qb

still conducts weakly to pull up voltage at node Q, Due to

the coupling effect of parasitic capacitances the voltage of

Qb, which is in the floating state, rises with node Q but

only slightly. In step 2, the data flipping finally takes

place when Q is strong enough to conduct the PDR tran-

sistor to discharge Qb do wn to the ground voltage.

It is worth mentioning that even though such a write

mechanism takes relatively longer time to accomplish the

data flipping, it is still shorter than the read access time,

and therefore, overall it do es not introduce any operating

frequency penalty. We can also further improve the cell’s

write-ability by strengthening the access transistors

(NA1 and NA2). It does not affect the read performance.

3.2.2. Read Operation

To perform a read operation, the wordline WL is en abled

and RWL is pulled down to ground to allow bitline dis-

charging. Assuming that the data stored at Q is now “0”.

Since data node Q and Qb are isolated from bitline BL

by PP2 and PP3 (which is between the true storage node

Q) and thus the so-called read current (which is the cur-

rent used to discharge a bitline) does not flow through

the storage node Qb but through the bypassing ND3 as

indicated in Figure 2. This is the main reason why the

read stability does not degrade at all in our cell. As for a

6T cell, the read current flows through the storage node

directly, thereby causing read disturbance, i.e., the volt-

age at data node Q will rise temporarily. This will de-

grade the read stability because the cell flipping will be

more likely to take place.

The pull-up transistors P1 and P2 are usually made

weaker for easy write operation just like in a conven-

tional 6T cell. While the pull-down transistors ND1 and

ND2, forming the cell discharging paths, need to be str-

onger to facilitate a larger read current and thereby a

quicker access. The pass gate transistors NA1 and NA2

need to be strong enough to serve as high-conduction pa-

ths between the accessed cell and the bitlines during both

the read and write op erations. The two pull-up transistors,

PP2 and PP3, need to be slightly stronger, to compensate

for the conductivity degradation of the cascaded PMOS

structure linking the storage nodes (i.e., Q and Qb) and

Vdd, which help contribute to a good hold SNM. Unlike

a 6T cell, the pull-down transistors do not have to be

strong, since they do not involve in the cell discharging

paths. However, their strengths are made comparable to

the cascaded PMOS structure mentioned above to ach-

ieve a more balanced cell structure which could lead to a

larger hold SNM.

In our cell we have seen that the SVNM has been

1.53times greater than that of conventional 6T cell. In

our cell we achieved 460mv while for 6T it is 300 mv.

The leakage power has also been reduced by 3.3 times

than that of conventional 6T.

Copyright © 2011 SciRes. CS