85

D. RATHEE ET AL.

prepared by mixin g TIP with absolute ethanol an d acetic

acid in the molar ratio of 0.1:8:0.1. The substrate was

placed on spinner and drops of above mentioned solution

were placed on substrate. The substrate was then allowed

to spin for 2 minutes with spinning rate 1500 rpm. Then

sample was baked for 20 minutes at 95˚C. The film was

than annealed in dynamic air at 550˚C for 30 minutes to

treat the adsorbed film. While SiO2 film was grown on

silicon substrate us ing dry oxidation process at 650˚C fo r

60 minutes with a pre ramp of 5˚C per minute so that we

reach reached to 950˚C and than flat temp of 950˚C for

the 110 minutes at last post-ramp of 5˚C per minutes for

60 minutes with N2(12) and O2(32).

2.2. MOS Capacitor Fabrication

MOS capacitors were fabricated on a 4 inch diameter &

800 micron thick N-type silicon wafer. The dielectric

layer of 510 Å was grown on silicon wafer by dry oxida-

tion at 950˚C for 2 hours. About 3000 Å of aluminum

was then deposited over oxide layers using the sputtering

technique. The 10–2 cm2 capacitor contact was defined by

physical mask. The contacts were annealed in gas at-

mosphere H2, & N2 at 350˚C for 25 minutes. The fabri-

cated capacitors electrically tested to characterize the

material and to inspect the device performance. The

variation of capacitance (C) with voltage VG ranging –5

Volts to +5 Volts is shown in Figure 2.

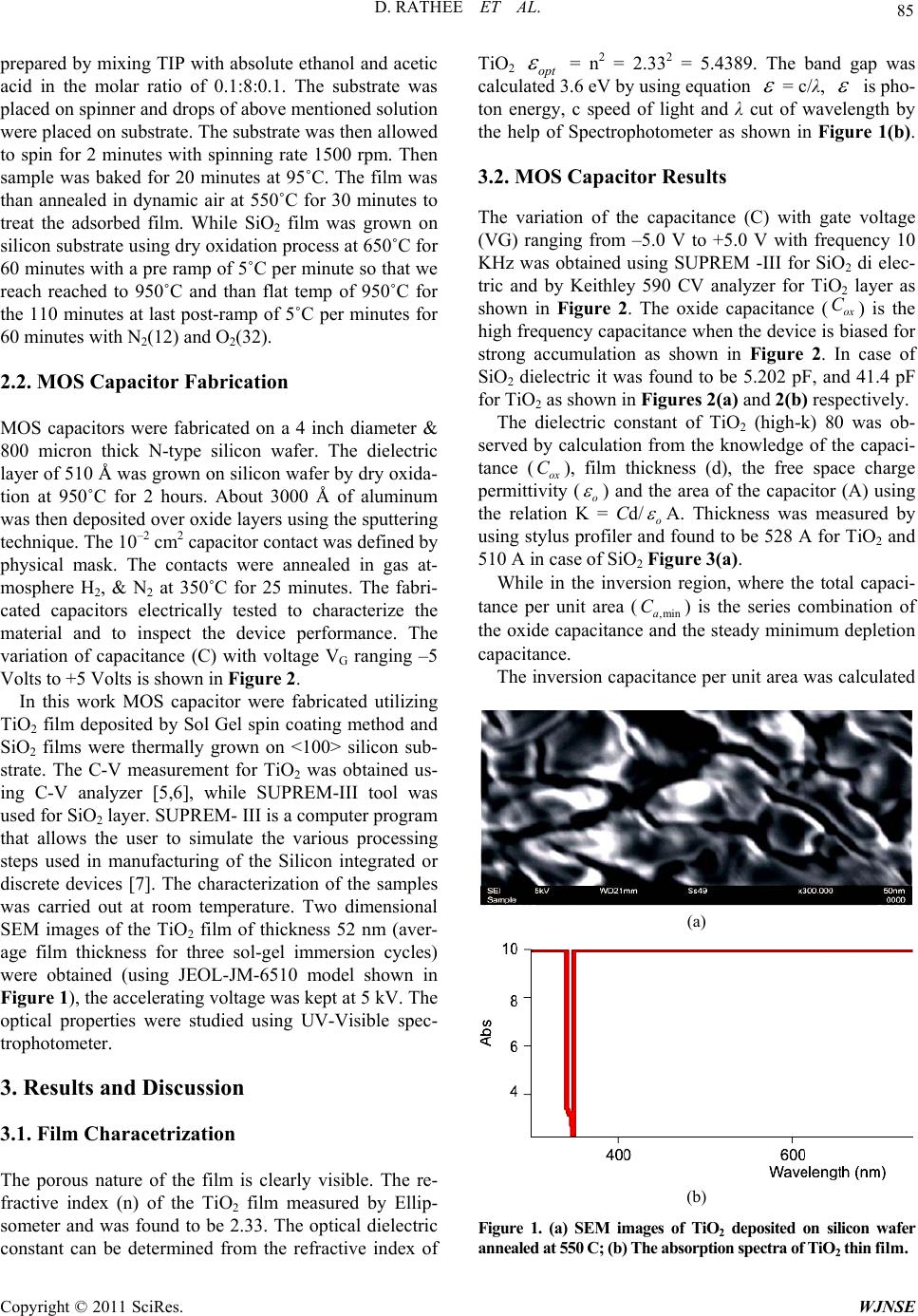

In this work MOS capacitor were fabricated utilizing

TiO2 film deposited by Sol Gel spin coating method and

SiO2 films were thermally grown on <100> silicon sub-

strate. The C-V measurement for TiO2 was obtained us-

ing C-V analyzer [5,6], while SUPREM-III tool was

used for SiO2 layer. SUPREM- III is a computer program

that allows the user to simulate the various processing

steps used in manufacturing of the Silicon integrated or

discrete devices [7]. The characterization of the samples

was carried out at room temperature. Two dimensional

SEM images of the TiO2 film of thickness 52 nm (aver-

age film thickness for three sol-gel immersion cycles)

were obtained (using JEOL-JM-6510 model shown in

Figure 1), the accelerating voltage was kept at 5 kV. The

optical properties were studied using UV-Visible spec-

trophotometer.

3. Results and Discussion

3.1. Film Characetrization

The porous nature of the film is clearly visible. The re-

fractive index (n) of the TiO2 film measured by Ellip-

someter and was found to be 2.33. The optical dielectric

constant can be determined from the refractive index of

TiO2 opt

= n2 = 2.332 = 5.4389. The band gap was

calculated 3.6 eV by using equation

= c/λ,

is pho-

ton energy, c speed of light and λ cut of wavelength by

the help of Spectrophotometer as shown in Figure 1(b).

3.2. MOS Capacitor Results

The variation of the capacitance (C) with gate voltage

(VG) ranging from –5.0 V to +5.0 V with frequency 10

KHz was obtained using SUPREM -III for SiO2 di elec-

tric and by Keithley 590 CV analyzer for TiO2 layer as

shown in Figure 2. The oxide capacitance () is the

high frequency capacitance when the device is biased for

strong accumulation as shown in Figure 2. In case of

SiO2 dielectric it was found to be 5.202 pF, and 41.4 pF

for TiO2 as shown in Figures 2(a) and 2(b) respectively.

ox

C

The dielectric constant of TiO2 (high-k) 80 was ob-

served by calculation from the knowledge of the capaci-

tance (ox ), film thickness (d), the free space charge

permittivity (o

C

) and the area of the capacitor (A) using

the relation K = Cd/ o

A. Thickness was measured by

using stylus profiler and found to be 528 A for TiO2 and

510 A in case of SiO2 Figure 3(a).

While in the inversion region, where the total capaci-

tance per unit area (,mina

C) is the series combination of

the oxide capacitance and the steady minimum depletion

capacitance.

The inversion capacitance per unit area was calculated

(a)

(b)

Figure 1. (a) SEM images of TiO2 deposited on silicon wafer

annealed at 550 C; (b) The absorption spectra of TiO2 t h i n f ilm.

Copyright © 2011 SciRes. WJNSE