216 S. MAHESHWARI ET AL.

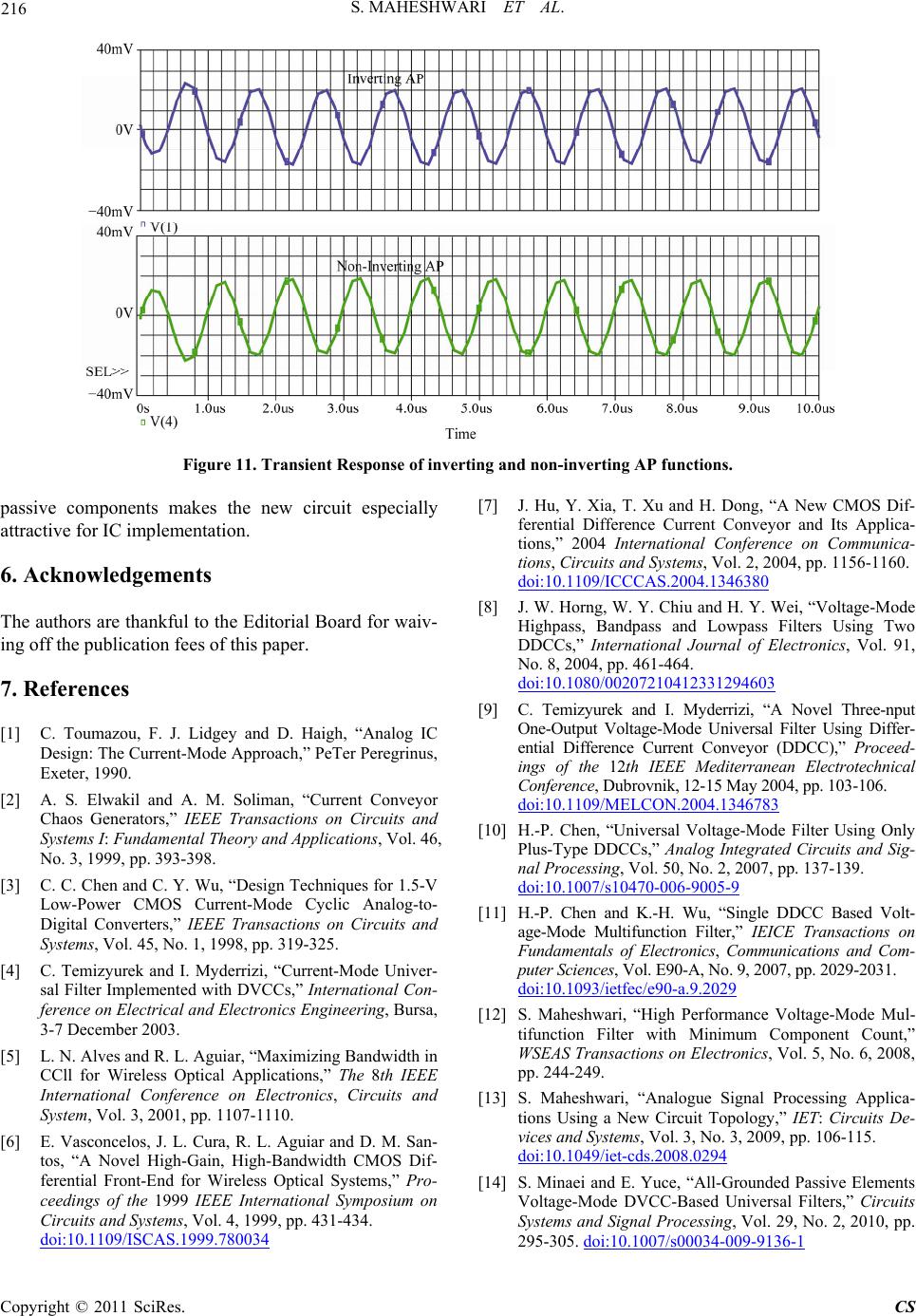

Figure 11. Transient Response of inverting and non-inverting AP functions.

passive components makes the new circuit especially

attractive for IC implementation.

6. Acknowledgements

The authors are thankful to the Editorial Board for waiv-

ing off the publication fees of this paper.

7. References

[1] C. Toumazou, F. J. Lidgey and D. Haigh, “Analog IC

Design: The Current-Mode Approach,” PeTer Peregrinus,

Exeter, 1990.

[2] A. S. Elwakil and A. M. Soliman, “Current Conveyor

Chaos Generators,” IEEE Transactions on Circuits and

Systems I: Fundamental Theory and Applications, Vol. 46,

No. 3, 1999, pp. 393-398.

[3] C. C. Chen and C. Y. Wu, “Design Techniques for 1.5-V

Low-Power CMOS Current-Mode Cyclic Analog-to-

Digital Converters,” IEEE Transactions on Circuits and

Systems, Vol. 45, No. 1, 1998, pp. 319-325.

[4] C. Temizyurek and I. Myderrizi, “Current-Mode Univer-

sal Filter Implemented with DVCCs,” International Con-

ference on Electrical and Electronics Engineering, Bursa,

3-7 December 2003.

[5] L. N. Alves and R. L. Aguiar, “Maximizing Bandwidth in

CCll for Wireless Optical Applications,” The 8th IEEE

International Conference on Electronics, Circuits and

System, Vol. 3, 2001, pp. 1107-1110.

[6] E. Vasconcelos, J. L. Cura, R. L. Aguiar and D. M. San-

tos, “A Novel High-Gain, High-Bandwidth CMOS Dif-

ferential Front-End for Wireless Optical Systems,” Pro-

ceedings of the 1999 IEEE International Symposium on

Circuits and Systems, Vol. 4, 1999, pp. 431-434.

doi:10.1109/ISCAS.1999.780034

[7] J. Hu, Y. Xia, T. Xu and H. Dong, “A New CMOS Dif-

ferential Difference Current Conveyor and Its Applica-

tions,” 2004 International Conference on Communica-

tions, Circuits and Systems, Vol. 2, 2004, pp. 1156-1160.

doi:10.1109/ICCCAS.2004.1346380

[8] J. W. Horng, W. Y. Chiu and H. Y. Wei, “Voltage-Mode

Highpass, Bandpass and Lowpass Filters Using Two

DDCCs,” International Journal of Electronics, Vol. 91,

o. 8, 2004, pp. 461-464.

doi:10.1080/00207210412331294603

[9] C. Temizyurek and I. Myderrizi, “A Novel Three-nput

One-Output Voltage-Mode Universal Filter Using Differ-

ential Difference Current Conveyor (DDCC),” Proceed-

ings of the 12th IEEE Mediterranean Electrotechnical

Conference, Dubrovnik, 12-15 May 2004, pp. 103-106.

doi:10.1109/MELCON.2004.1346783

[10] H.-P. Chen, “Universal Voltage-Mode Filter Using Only

Plus-Type DDCCs,” Analog Integrated Circuits and Sig-

nal Processing, Vol. 50, No. 2, 2007, pp. 137-139.

doi:10.1007/s10470-006-9005-9

[11] H.-P. Chen and K.-H. Wu, “Single DDCC Based Volt-

age-Mode Multifunction Filter,” IEICE Transactions on

Fundamentals of Electronics, Communications and Com-

puter Sciences, Vol. E90-A, No. 9, 2007, pp. 2029-2031.

doi:10.1093/ietfec/e90-a.9.2029

[12] S. Maheshwari, “High Performance Voltage-Mode Mul-

tifunction Filter with Minimum Component Count,”

WSEAS Transactions on Electronics, Vol. 5, No. 6, 2008,

pp. 244-249.

[13] S. Maheshwari, “Analogue Signal Processing Applica-

tions Using a New Circuit Topology,” IET: Circuits De-

vices and Systems, Vol. 3, No. 3, 2009, pp. 106-115.

doi:10.1049/iet-cds.2008.0294

[14] S. Minaei and E. Yuce, “All-Grounded Passive Elements

Voltage-Mode DVCC-Based Universal Filters,” Circuits

Systems and Signal Processing, Vol. 29, No. 2, 2010, pp.

295-305. doi:10.1007/s00034-009-9136-1

Copyright © 2011 SciRes. CS