M. KUMAR ET AL.

Copyright © 2011 SciRes. CS

194

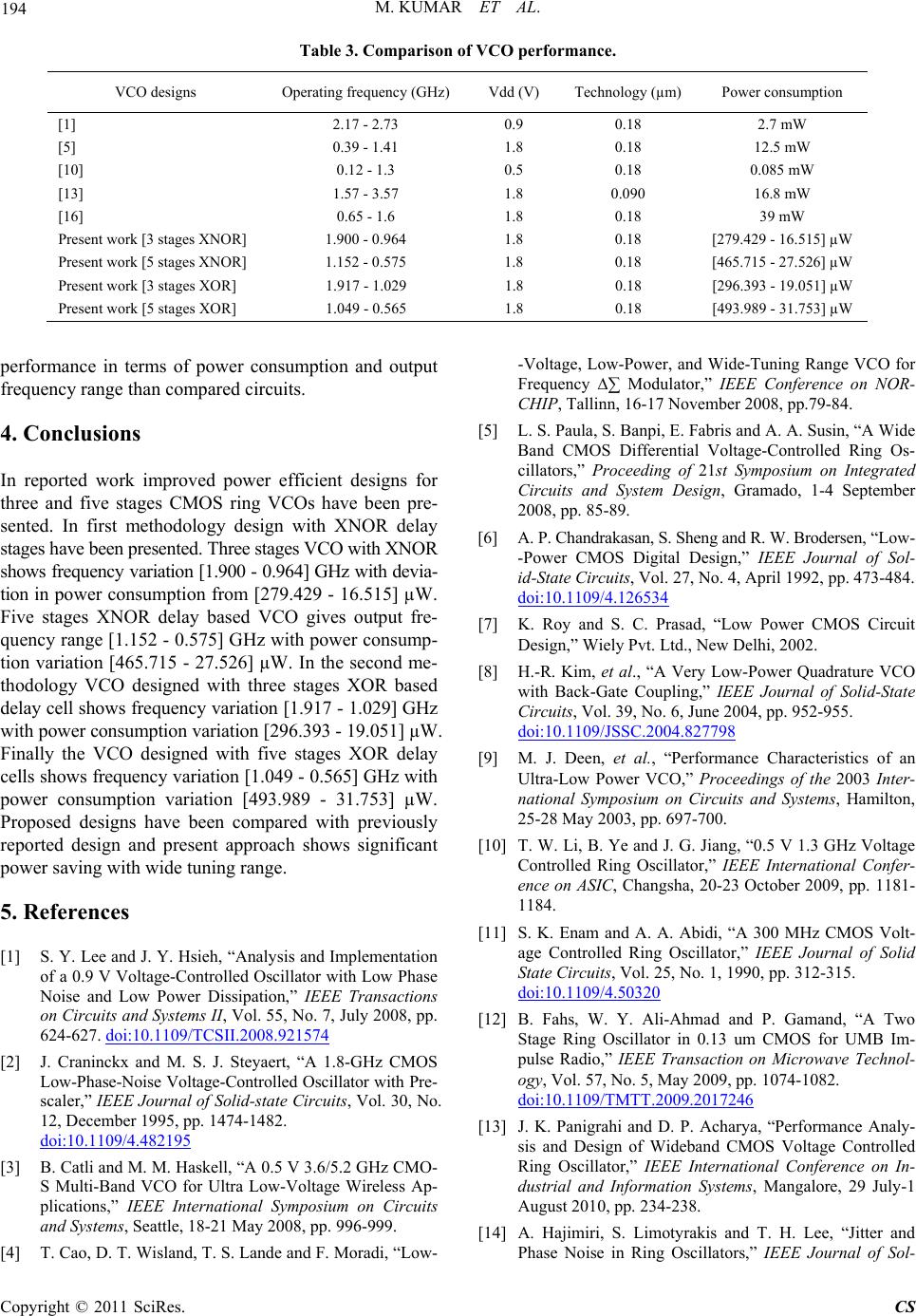

Table 3. Comparison of

VCO performance.

Vdd (V) Technology (µm) Power consumption VCO designs Operating frequency (GHz)

[1] 2.17 - 2.73 0.9 0.18 2.7 mW

[5] 0.39 - 1.41 1.8 0.18 12.5 mW

[10] 0.12 - 1.3 0.5 0.18 0.085 mW

[13] 16.8 mW

[16] 0.65 - 1.6 1.8 0.18 39 mW

Present work [3 stages XNOR] [

ent work [5 stages XNOR] 1 [465.7

ent work [3 stages XOR] [296.3 µW

nt work [5 stages XOR] 1. [493. µW

1.57 - 3.57 1.8 0.090

1.900 - 0.964 1.8 0.18 279.429 - 16.515] µW

Pres.152 - 0.575 1.8 0.18 15 - 27.526] µW

Pres1.917 - 1.029 1.8 0.18 93 - 19.051]

Prese049 - 0.5651.8 0.18 989 - 31.753]

perform in terms of power consumptiotput

frequenircuits.

4. Con

reported work improved power efficient designs for

CO with XNOR

iation [1.900 - 0.964] GHz with devia-

ption from [279.429 - 16.515] µW.

o. 7, July 2008, pp.

8.921574

ancen and ou

cy range than compared c

clusions

In

three and five stages CMOS ring VCOs have been pre-

sented. In first methodology design with XNOR delay

ages have been presented. Three stages Vst

shows frequency var

on in power consumti

Five stages XNOR delay based VCO gives output fre-

quency range [1.152 - 0.575] GHz with power consump-

tion variation [465.715 - 27.526] µW. In the second me-

thodology VCO designed with three stages XOR based

delay cell shows frequency variation [1.917 - 1.029] GHz

with power consumption variation [296.393 - 19.051] µW.

Finally the VCO designed with five stages XOR delay

cells shows frequency variation [1.049 - 0.565] GHz with

power consumption variation [493.989 - 31.753] µW.

Proposed designs have been compared with previously

reported design and present approach shows significant

power saving with wide tuning range.

5. References

[1] S. Y. Lee and J. Y. Hsieh, “Analysis and Implementation

of a 0.9 V Voltage-Controlled Oscillator with Low Phase

Noise and Low Power Dissipation,” IEEE Transactions

on Circuits and Systems II, Vol. 55, N

624-627. doi:10.1109/TCSII.200

nd M. S. J. Steyaert, “A 1.8-GHz CM

Low-Phase-Noise Voltage-Controlled Oscillator with Pre-

[2] J. Craninckx aOS

scaler,” IEEE Journal of Solid-state Circuits, Vol. 30, No.

12, December 1995, pp. 1474-1482.

doi:10.1109/4.482195

[3] B. Catli and M. M. Haskell, “A 0.5 V 3.6/5.2 GHz CMO-

S Multi-Band VCO for Ultra Low-Voltage Wireless Ap-

oltage, Lower, and Wide-Tange VCO for

equency ∆∑ dulator,” n NOR-

IP, Tallinn7 Nove

[5] S. Paula, Si, E. Fa

nd CMOSrential ing Os-

cillators,” Proceeding of 21st Symposium on Integrated

September

plications,” IEEE International Symposium on Circuits

and Systems, Seattle, 18-21 May 2008, pp. 996-999.

[4] T. Cao, D. T. Wisland, T. S. Lande and F. Moradi, “Low-

Circuits and System Design, Gramado, 1-4

2008, pp. 85-89.

-V-Powuning R

Fr Mo IEEE Conference o

CH , 16-1mber 2008, pp.79-84.

L.. Banpbris and A. A. Susin, “A Wide

Ba DiffeVoltage-Controlled R

[6] A. P. Chandrakasan, S. Sheng and R. W. Brodersen, “Low-

-Power CMOS Digital Design,” IEEE Journal of Sol-

id-State Circuits, Vol. 27, No. 4, April 1992, pp. 473-484.

doi:10.1109/4.126534

[7] K. Roy and S. C. Prasad, “Low Power CMOS Circuit

Design,” Wiely Pvt. Ltd., New Delhi, 2002.

[8] H.-R. Kim, et al., “A Very Low-Power Quadrature VCO

with Back-Gate Coupling,” IEEE Journal of Solid-State

Circuits, Vol. 39, No. 6, June 2004, pp. 952-955.

doi:10.1109/JSSC.2004.827798

[9] M. J. Deen, et al., “Performance Characteristics of an

Ultra-Low Power VCO,” Proceedings of the 2003 Inter-

national Symposium on Circuits and Systems, Hamilton,

25-28 May 2003, pp. 697-700.

[10] T. W. Li, B. Ye and J. G. Jiang, “0.5 V 1.3 GHz Voltage

Controlled Ring Oscillator,” IEEE International Confer-

ence on ASIC, Changsha, 20-23 October 2009, pp. 1181-

1184.

[11] S. K. Enam and A. A. Abidi, “A 300 MHz CMOS Volt-

age Controlled Ring Oscillator,” IEEE Journal of Solid

State Circuits, Vol. 25, No. 1, 1990, pp. 312-315.

doi:10.1109/4.50320

[12] B. Fahs, W. Y. Ali-Ahmad and P. Gamand, “A Two

Stage Ring Oscillator in 0.13 um CMOS for UMB Im-

pulse Radio,” IEEE Transaction on Microwave Technol-

ogy, Vol. 57, No. 5, May 2009, pp. 1074-1082.

doi:10.1109/TMTT.2009.2017246

[13] J. K. Panigrahi and D. P. Acharya, “Performance Analy-

sis and Design of Wideband CMOS Voltage Controlled

Ring Oscillator,” IEEE International Conference on In-

dustrial and Information Systems, Mangalore, 29 July-1

August 2010, pp. 234-238.

[14] A. Hajimiri, S. Limotyrakis and T. H. Lee, “Jitter and

Phase Noise in Ring Oscillators,” IEEE Journal of Sol-