184 A. AHMADPOUR

prove the system’s quality, especially in very unfriendly

environments such as mixed-mode applications. How-

ever, at lower supply voltages, pseudo differential OTAs

could be used to avoid the voltage drop across the tail

current source used in the fully differential structures.

Taking the tail current source achieves a larger signal

swing, but it also results in larger CM gain. So it requires

to carefully controlling the CM response for pseudo dif-

ferential OTAs. The reduced supply voltage will cause

many problems when designing analog circuits due to

the reduction in available signal swing. This problem is

magnified due to the fact that the threshold voltage (VT)

of the transistors has been reduced at a slower rate than

the supply voltage. In other words, the threshold-voltage

with decreasing the Power supply never reduces linearly.

If standard analog design techniques continue to be used,

the dynamic range and SNR of the circuits will degrade.

The gain of devices such as amplifiers will also decrease

because cascode transistors can no longer be used since

they limit the output swing. The design of rail-to-rail

input circuits is also made more difficult due to the large

VT which must be overcome. One solution for designing

low-voltage analog circuits is to operate the transistors in

the weak inversion region. The drawbacks to this tech-

nique include a limited input signal swing, an increase in

the mismatch between transistors, a low slew-rate due to

the low bias current levels, and large transistor sizes

[3-6]. In order to avoid these drawbacks a bulk-input

technique can be used, which allows for operation in the

moderate inversion region at supply voltages equal to the

VT of the technology. The voltage applied to the bulk

actually reduces the threshold voltage of the transistor,

which increases the inversion level. One drawback of the

bulk input technique is that the input transistor must sit

in an n-well or p-well, so that its bulk is separate from

the bulk of the rest of the transistors. This is not a prob-

lem in advanced technologies, which make use of triple

well structures. In triple-well processes both the NMOS

and PMOS can have isolated bulk terminals [5]. This

paper presents the design of a novel two-stage bulk-input

pseudo differential OTA, which operates at a supply

voltage of 0.5 V. The circuit was designed using the

90 nm process in digital CMOS technology. Design pro-

cedure for this new merged OTA structure such as main

OTA, CMFB and bias circuits are introduced in Section

2. In Section 3, SC integrator and active RC filter design

are described. Section 4 presents simulation results. Fi-

nally, conclusions and acknowledge are given in Section

5 and 6, respectively.

2. Bulk-Input OTA Circuit Design

2.1. Main Amplifier

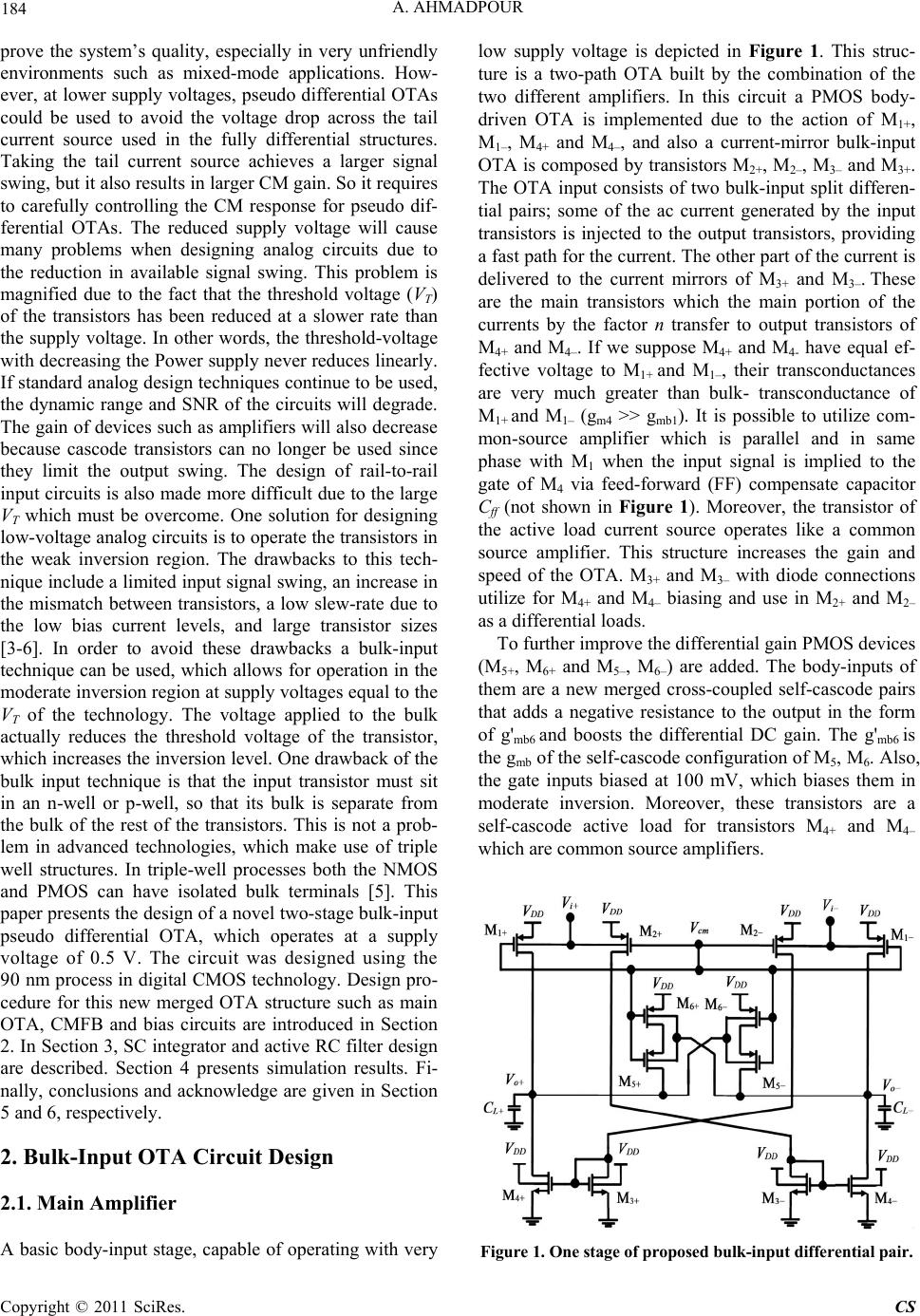

A basic body-input stage, capable of operating with very

low supply voltage is depicted in Figure 1. This struc-

ture is a two-path OTA built by the combination of the

two different amplifiers. In this circuit a PMOS body-

driven OTA is implemented due to the action of M1+,

M1–, M4+ and M4–, and also a current-mirror bulk-input

OTA is composed by transistors M2+, M2–, M3– and M3+.

The OTA input consists of two bulk-input split differen-

tial pairs; some of the ac current generated by the input

transistors is injected to the output transistors, providing

a fast path for the current. The other part of the current is

delivered to the current mirrors of M3+ and M3–. These

are the main transistors which the main portion of the

currents by the factor n transfer to output transistors of

M4+ and M4–. If we suppose M4+ and M4- have equal ef-

fective voltage to M1+ and M1–, their transconductances

are very much greater than bulk- transconductance of

M1+ and M1– (gm4 >> gmb1). It is possible to utilize com-

mon-source amplifier which is parallel and in same

phase with M1 when the input signal is implied to the

gate of M4 via feed-forward (FF) compensate capacitor

Cff (not shown in Figure 1). Moreover, the transistor of

the active load current source operates like a common

source amplifier. This structure increases the gain and

speed of the OTA. M3+ and M3– with diode connections

utilize for M4+ and M4– biasing and use in M2+ and M2–

as a differential loads.

To further improve the differential gain PMOS devices

(M5+, M6+ and M5–, M6–) are added. The body-inputs of

them are a new merged cross-coupled self-cascode pairs

that adds a negative resistance to the output in the form

of g'mb6 and boosts the differential DC gain. The g'mb6 is

the gmb of the self-cascode configuration of M5, M6. Also,

the gate inputs biased at 100 mV, which biases them in

moderate inversion. Moreover, these transistors are a

self-cascode active load for transistors M4+ and M4–

which are common source amplifiers.

Figure 1. One stage of p rop os ed bu lk - inpu t d ifferential pair.

Copyright © 2011 SciRes. CS