Circuits and Systems, 2011, 2, 145-150

doi:10.4236/cs.2011.23022 Published Online July 2011 (http://www.SciRP.org/journal/cs)

Copyright © 2011 SciRes. CS

New Analysis to Measure the Capacitance and

Conductance of MOS Structure toward Small Size of

VLSI Circuits

Wagah Farman Mohammad

Communications & Electronics Department, Faculty of Engineering, Philadelphia University, Amman, Jordan

E-mail: wagahfaljubori@yahoo.com

Received February 16, 2011; revised April 15, 2011; accepted April 22, 2011

Abstract

In this research thin film layers have been prepared at alternate layers of resistive and dielectric deposited on

appropriate substrates to form four - terminal R-Y-NR network. If the gate of the MOS structures deposited

as a strip of resistor film like NiCr, the MOS structure can be analyzed as R-Y-NR network. A method of

analysis has been proposed to measure the shunt capacitance and the shunt conductance of certain MOS

samples. Mat lab program has been used to compute shunt capacitance and shunt conductance at different

frequencies. The results computed by this method have been compared with the results obtained by LCR

meter method and showed perfect coincident with each other.

Keywords: Thin Film R-Y-NR Network, MOS R-Y-NR Network, MOS-VLSI Circuits, MOS Capacitance

1. Introduction

In recent years, there have been rapidly growing interest

and activity in thin film integrated circuits as an ap-

proach to microelectronics. Electronic circuits have been

fabricated on the basis of replacing conventional lumped

elements with their thin film equivalents. Essentially the

VLSI memory devices are Electronic structures. The

Metal-Oxide-Silicon (MOS) structures are an important

type of the VLSI memory devises. MOS capacitance is

one of the key test structures for VLSI technology char-

acterization. It permits the determination of the electrical

characteristics of a given technology such as oxide

thickness, substrate doping, the switching speed and the

driving capability of VLSI circuits [1].

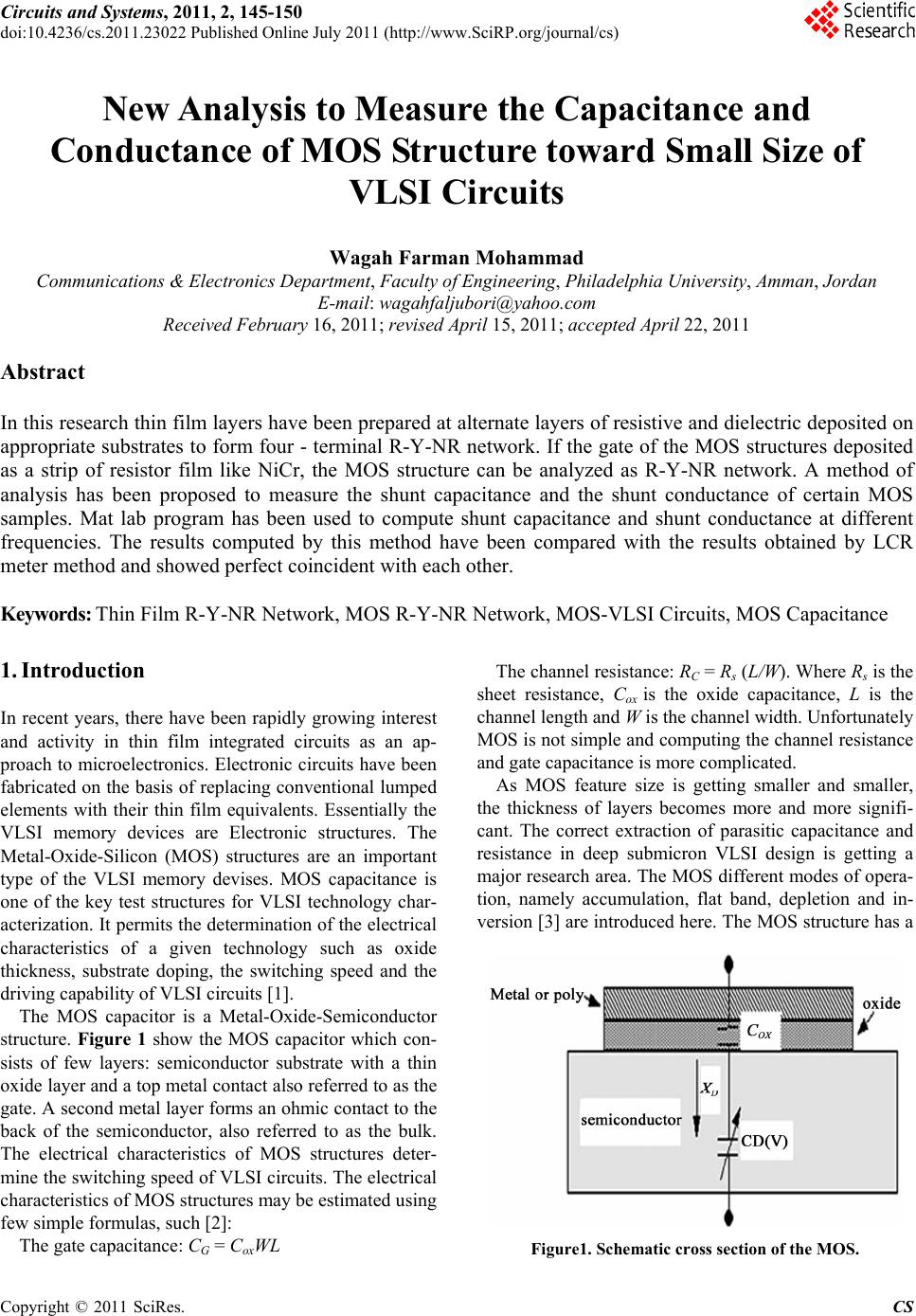

The MOS capacitor is a Metal-Oxide-Semiconductor

structure. Figure 1 show the MOS capacitor which con-

sists of few layers: semiconductor substrate with a thin

oxide layer and a top metal contact also referred to as the

gate. A second metal layer forms an ohmic contact to the

back of the semiconductor, also referred to as the bulk.

The electrical characteristics of MOS structures deter-

mine the switching speed of VLSI circuits. The electrical

characteristics of MOS structures may be estimated using

few simple formulas, such [2]:

The gate capacitance: CG = CoxWL

The channel resistance: RC = Rs (L/W). Where Rs is the

sheet resistance, Cox is the oxide capacitance, L is the

channel length and W is the channel width. Unfortunately

MOS is not simple and computing the channel resistance

and gate capacitance is more complicated.

As MOS feature size is getting smaller and smaller,

the thickness of layers becomes more and more signifi-

cant. The correct extraction of parasitic capacitance and

resistance in deep submicron VLSI design is getting a

major research area. The MOS different modes of opera-

tion, namely accumulation, flat band, depletion and in-

version [3] are introduced here. The MOS structure has a

Figure1. Schematic cross section of the MOS.