B. P. DAS ET AL.

Copyright © 2011 SciRes. EPE

134

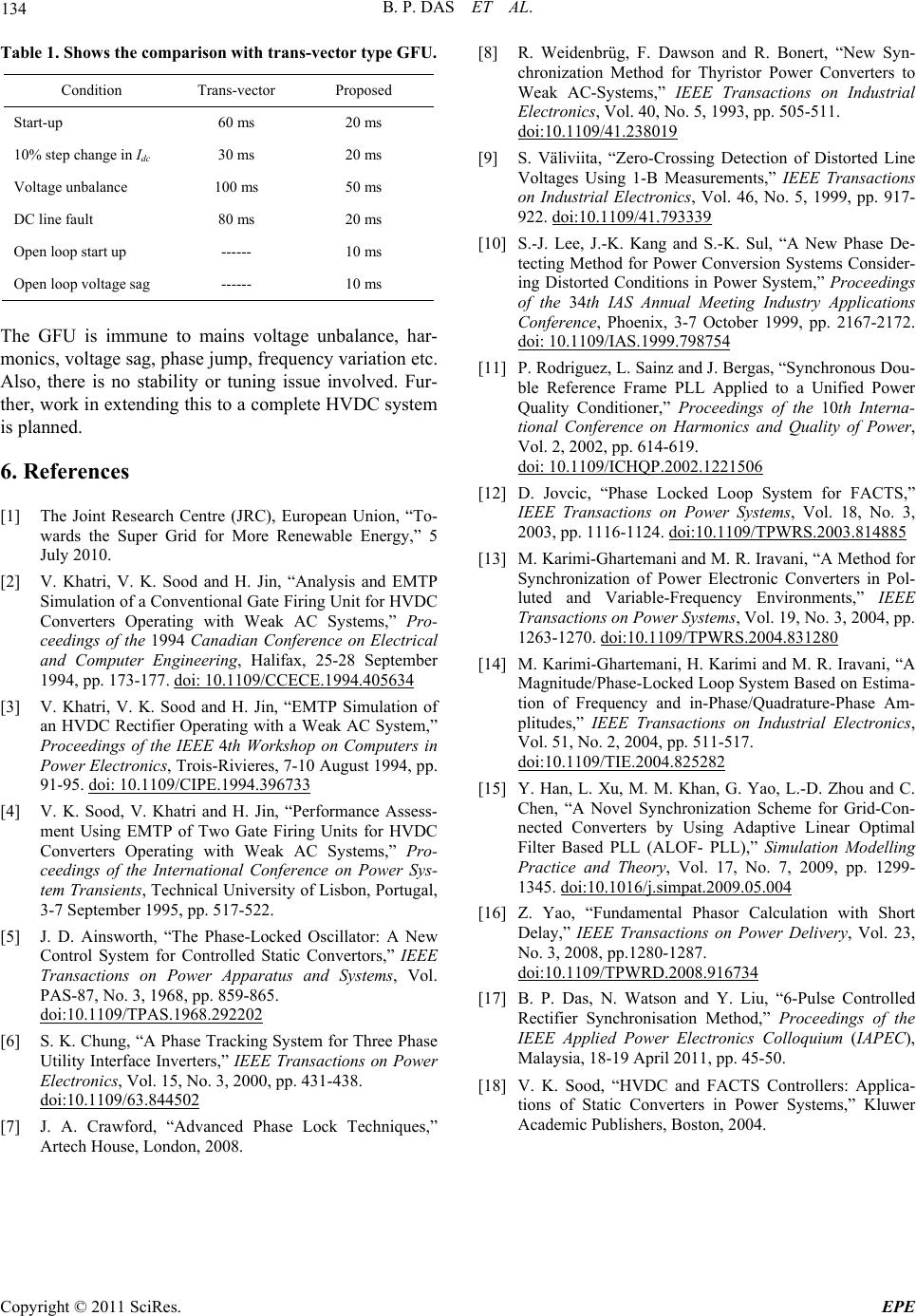

Table 1. Shows the comparison with trans-vector type GFU.

Condition Trans-vector Proposed

Start-up 60 ms 20 ms

10% step change in Idc 30 ms 20 ms

Voltage unbalance 100 ms 50 ms

DC line fault 80 ms 20 ms

Open loop start up ------ 10 ms

Open loop voltage sag ------ 10 ms

The GFU is immune to mains voltage unbalance, har-

monics, voltage sag, phase jump, frequency variation etc.

Also, there is no stability or tuning issue involved. Fur-

ther, work in extending this to a complete HVDC system

is planned.

6. References

[1] The Joint Research Centre (JRC), European Union, “To-

wards the Super Grid for More Renewable Energy,” 5

July 2010.

[2] V. Khatri, V. K. Sood and H. Jin, “Analysis and EMTP

Simulation of a Conventional Gate Firing Unit for HVDC

Converters Operating with Weak AC Systems,” Pro-

ceedings of the 1994 Canadian Conference on Electrical

and Computer Engineering, Halifax, 25-28 September

1994, pp. 173-177. doi: 10.1109/CCECE.1994.405634

[3] V. Khatri, V. K. Sood and H. Jin, “EMTP Simulation of

an HVDC Rectifier Operating with a Weak AC System,”

Proceedings of the IEEE 4th Workshop on Computers in

Power Electronics, Trois-Rivieres, 7-10 August 1994, pp.

91-95. doi: 10.1109/CIPE.1994.396733

[4] V. K. Sood, V. Khatri and H. Jin, “Performance Assess-

ment Using EMTP of Two Gate Firing Units for HVDC

Converters Operating with Weak AC Systems,” Pro-

ceedings of the International Conference on Power Sys-

tem Transients, Technical University of Lisbon, Portugal,

3-7 September 1995, pp. 517-522.

[5] J. D. Ainsworth, “The Phase-Locked Oscillator: A New

Control System for Controlled Static Convertors,” IEEE

Transactions on Power Apparatus and Systems, Vol.

PAS-87, No. 3, 1968, pp. 859-865.

doi:10.1109/TPAS.1968.292202

[6] S. K. Chung, “A Phase Tracking System for Three Phase

Utility Interface Inverters,” IEEE Transactions on Power

Electronics, Vol. 15, No. 3, 2000, pp. 431-438.

doi:10.1109/63.844502

[7] J. A. Crawford, “Advanced Phase Lock Techniques,”

Artech House, London, 2008.

[8] R. Weidenbrüg, F. Dawson and R. Bonert, “New Syn-

chronization Method for Thyristor Power Converters to

Weak AC-Systems,” IEEE Transactions on Industrial

Electronics, Vol. 40, No. 5, 1993, pp. 505-511.

doi:10.1109/41.238019

[9] S. Väliviita, “Zero-Crossing Detection of Distorted Line

Voltages Using 1-B Measurements,” IEEE Transactions

on Industrial Electronics, Vol. 46, No. 5, 1999, pp. 917-

922. doi:10.1109/41.793339

[10] S.-J. Lee, J.-K. Kang and S.-K. Sul, “A New Phase De-

tecting Method for Power Conversion Systems Consider-

ing Distorted Conditions in Power System,” Proceedings

of the 34th IAS Annual Meeting Industry Applications

Conference, Phoenix, 3-7 October 1999, pp. 2167-2172.

doi: 10.1109/IAS.1999.798754

[11] P. Rodriguez, L. Sainz and J. Bergas, “Synchronous Dou-

ble Reference Frame PLL Applied to a Unified Power

Quality Conditioner,” Proceedings of the 10th Interna-

tional Conference on Harmonics and Quality of Power,

Vol. 2, 2002, pp. 614-619.

doi: 10.1109/ICHQP.2002.1221506

[12] D. Jovcic, “Phase Locked Loop System for FACTS,”

IEEE Transactions on Power Systems, Vol. 18, No. 3,

2003, pp. 1116-1124. doi:10.1109/TPWRS.2003.814885

[13] M. Karimi-Ghartemani and M. R. Iravani, “A Method for

Synchronization of Power Electronic Converters in Pol-

luted and Variable-Frequency Environments,” IEEE

Transactions on Power Systems, Vol. 19, No. 3, 2004, pp.

1263-1270. doi:10.1109/TPWRS.2004.831280

[14] M. Karimi-Ghartemani, H. Karimi and M. R. Iravani, “A

Magnitude/Phase-Locked Loop System Based on Estima-

tion of Frequency and in-Phase/Quadrature-Phase Am-

plitudes,” IEEE Transactions on Industrial Electronics,

Vol. 51, No. 2, 2004, pp. 511-517.

doi:10.1109/TIE.2004.825282

[15] Y. Han, L. Xu, M. M. Khan, G. Yao, L.-D. Zhou and C.

Chen, “A Novel Synchronization Scheme for Grid-Con-

nected Converters by Using Adaptive Linear Optimal

Filter Based PLL (ALOF- PLL),” Simulation Modelling

Practice and Theory, Vol. 17, No. 7, 2009, pp. 1299-

1345. doi:10.1016/j.simpat.2009.05.004

[16] Z. Yao, “Fundamental Phasor Calculation with Short

Delay,” IEEE Transactions on Power Delivery, Vol. 23,

No. 3, 2008, pp.1280-1287.

doi:10.1109/TPWRD.2008.916734

[17] B. P. Das, N. Watson and Y. Liu, “6-Pulse Controlled

Rectifier Synchronisation Method,” Proceedings of the

IEEE Applied Power Electronics Colloquium (IAPEC),

Malaysia, 18-19 April 2011, pp. 45-50.

[18] V. K. Sood, “HVDC and FACTS Controllers: Applica-

tions of Static Converters in Power Systems,” Kluwer

Academic Publishers, Boston, 2004.