Circuits and Systems

Vol.06 No.03(2015), Article ID:54990,11 pages

10.4236/cs.2015.63008

Implementation & Comparative Analysis of 10, 18 & 24 Level Diode Clamped Inverters Using “Trust Region Dog Leg” Method

Haider Ali1, Mohamed Z. H. Qawaqzeh2, Muhammad Abbas1, Takialddin Al Smadi3

1CIIT, Abbottabad, Pakistan

2Faculty of Engineering, Al-Balqa’ Applied University, Amman, Jordan

3Department of Communications and Electronics Engineering, College of Engineering, Jerash University, Jerash, Jordan

Email: haiderali@ciit.net.pk, qawaqzeh@hotmail.com

Copyright © 2015 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received 5 December 2014; revised 23 March 2015; published 25 March 2015

ABSTRACT

Multilevel inverters are used in many industrial applications because of good power quality, minimum losses and less harmonics contents. Multilevel inverters require no series connected synchronized switching devices, transformer and complex filters. In this paper 10, 18, 24 diode clamped multi-level inverters (DCMLI) are implemented using trust region dog leg optimization method to find the optimized values of switching angles (θ). It decreases the total harmonic distortion (THD) of the output voltages and to reduce the complexity of external filter required. The multi-level inverters are implemented in MATLAB Simulation and results are compared in terms of harmonics, system complexity and efficiency.

Keywords:

DCMLI, THD, Switching Angles, IGBTs, Trust Region Dog Leg

1. Introduction

Different techniques like Sinusoidal pulse width modulation (SPWM), SVPWM and multilevel inverters are used for the conversion of DC into AC power [1] . Numerous techniques of multi-level inverters are implemented to improve the power quality and harmonic distortion [2] . 5-level cascaded multi-level inverter implemented for power quality improvement using DSTATCOM with isolated energy for DC storage [3] . A chopper circuit with the flying capacitor voltage diode clamped for alignment of multilevel inverters reduces chopper frequency and voltage to AC voltage multilevel production [4] . 5-level diode clamped inverter for electric machines, working at high speed with the power of twelve [5] . 3-level diode clamped inverter with active neutral points and zero current transition (3 tests such as pre-employment) use it for sustainable energy [6] .

Comparison between two diodes clamped inverter nerve point of converter (DNPC-3 l tests such as pre- employment) and (ANPC-3 l tests such as pre-employment) discussed options for switching energy volume [7] . Using capacitors and one DC source to build multilevel inverter cascaded (H-bridge) [8] .

H-bridge multilevel inverter flying capacitor using two different schemes of voltage balancing and equations used [9] . The closed method based on carrier to minimize losses of switches for a half cycle of the basic wave is used for analyzing each half-cycle of the switch area [10] . Two SVM methods are executed that explosive for the purpose of controlling the DVR in order to reduce the losses in the circuit breakers and less harmonic DIS [11] . Particle Swarm Optimization used in cascade inverter to reduce harmonics improve output quality [12] . Cascade multilevel inverter is implemented by using the theory of vector space to switch strategies in the topology. The proposed topology reduces harmonic distortion and switching frequency employed switches [13] .

This proposed converter, diodes clamped multilevel inverters (DCMLI) for different levels of switching angles are calculated using the dog leg in order to minimize the total harmonic distortion (THD), improve the quality of the electricity voltage wave form, the overall efficiency of the inverter, as well as to study the relations of levels with THD.

2. Methodology

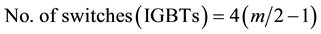

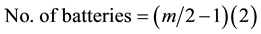

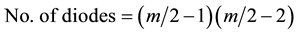

Circuit diagrams of diode clamped multilevel inverters (DCMLI) 10, 18, 24 levels are shown in the Figures 1-3 respectively. DCMLI consists of two legs and each leg consists of two sub-systems connected in series. Each subsystem comprises  switches. Every level of multilevel inverter has its own requirement of numbers of switches (IGBTs), batteries and clamping diodes. The components are calculated using Equations (1), (2) and (3) and shown in Table 1.

switches. Every level of multilevel inverter has its own requirement of numbers of switches (IGBTs), batteries and clamping diodes. The components are calculated using Equations (1), (2) and (3) and shown in Table 1.

(1)

(1)

(2)

(2)

(3)

(3)

Switches of subsystem 1 are connected in series with subsystem 2 in one leg and similarly subsystem 3 with subsystem 4 in other leg. The output of the DCMLI is stepped stair case voltage levels as shown in Figure 5 for 10 levels DCMLI. To obtain different voltage levels and to eliminate lower order harmonics such as 3rd, 5th, 7th, 11th and 13th, selective harmonic elimination technique is implemented using Trust Region Dog Leg, the flow diagram is shown in Figure 4. Dogleg utilizes Newton and steepest descent methods. The combination of these

Figure 1. 10 level DCMLI.

Figure 2. 18 level DCMLI.

Table 1. Number of components required for DCMLI.

two methods ensures a fast convergence and a solution of function in the steepest descent direction. The second step involves finding the value of trust region radius to estimate length of step for the current iteration such that the following condition is obeyed. Trust region dog leg optimization technique is utilized to find out the optimized switching angles using a set of non-linear equations derived to selectively eliminate specific harmonics (Selective Harmonic Elimination). The set of non-linear equations are shown in Equations (14), (15) and (16) and trust region dog leg method determines the optimized switching angles to result a wave form with minimum Total Harmonic Distortion (THD).

For particular switching angle different switches are turned on, for 10 levels four switches and 8 for 18 levels and 11 for 24 levels are on in one leg and 4, 8 and 11 in another leg. Every switch is turned on and off only once in half cycle therefore the switching losses are low. Table 2 is showing the switching states for one leg 10 levels DCMLI.

For positive cycle all switches of subsystem 3 are OFF and sub system 4 are ON. For negative cycle, switches

Figure 3. 24 level DCMLI.

Figure 4. Trust region dogleg flow diagram.

Figure 5. Output of 10 levels DCMLI.

Table 2. On-off switching pattern for 10 Level DCMLI.

of subsystem 3 and subsystem 4 are ON and OFF in the similar way and all switches of sub system 1 are OFF and subsystem’s 2 are ON. Similarly switching states of 18 and 24 levels are shown in Table 3, Table 4.

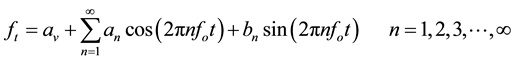

As shown in Figure 5 each half cycle of the output voltage is divided into multi-levels for optimized switching angles . The switching angles are determined using Fourier series to find system of non-linear equations and further “trust region dogleg” method is applied. Fourier series is applied first to find out a set of non-linear equations.

. The switching angles are determined using Fourier series to find system of non-linear equations and further “trust region dogleg” method is applied. Fourier series is applied first to find out a set of non-linear equations.

From Fourier series the periodic function can be expressed as following

(4)

(4)

,

,  and

and  are Fourier coefficient and can be determined from following equations

are Fourier coefficient and can be determined from following equations

Here T is the fundamental period and

Multi-level inverters have odd quarter wave symmetry so they posse both odd and half wave symmetry. The Fourier coefficient for odd quarter wave symmetry simplifies to

Table 3. Switching states of 18 levels DCMLI.

Table 4. Switches state of both legs of 24 levels DCMLI.

As

Integrating Equation (12) W.R.T switching angles

Equation (13) shows odd harmonics in DCMLI as switching angles. To eliminate 3rd, 5th, 7th, 9th, 11th and 13th harmonics and output peak voltage is controlled to v, harmonics equations results in

The values of switching angles can be calculated from these set of non-linear equations using iterative method.

Equation (14) can also be written as

where

Modulation index

s = No. of DC sources.

The total harmonic distortion is calculated from the following equation

Computed values of switching angles in radians of 10, 18 and 24 levels DCMLI when dog leg method is applied are Tables 5-7.

3. Results

Total harmonic distortion values and output voltage wave forms are observed for m = 0.9 and the variation in harmonics and the quality of output waveforms. The value of m is kept constant while total numbers of voltage levels in half cycle (0 - π) of output waveforms are increased gradually, when Voltage levels are increased the

Table 5. Switching angles of 10 levels DCMLI.

Table 6. Switching angles of 18 levels inverter.

Table 7. Switching angles of 24 levels inverter.

wave form gets closer to pure sinusoidal wave form and consequently the percent total harmonic distortion decreases. Total harmonic distortion (THD) depends on the 3rd, 5th, 7th, 9th, 11th, and 13th (in the proposed case) lower harmonics when levels are increased the harmonics results smaller peak values which decreases the THD value as shown in Table 8 and Figures 6-11 for various levels.

4. Conclusion

Trust region dog leg method employing optimized switching angles has reduced total harmonic distortion in multilevel inverters compared to when non-optimized switching angles are considered. It is evident from the

Table 8. THD values for DCMI.

Figure 6. Output voltage of 10 levels DCMLI.

Figure 7. Frequency spectrum & THD of 10 levels DCMLI.

Figure 8. Output voltage of 18 levels DCMLI.

Figure 9. THD of 18 levels DCMLI.

Figure 10. Output voltage of 24 levels DCMLI.

Figure 11. THD of 24 levels DCMLI.

results that an increasing number of voltage levels in the output waveforms decrease the total harmonic distortion (THD) and the output wave form gets closer to pure sinusoidal voltage plus overall efficiency of the system rises. Moreover, the number of battery sources, IGBTs and diodes required makes the system bulkier and expensive as the number of levels is increased but ensures a sooth input to the industrial load (e.g. AC Motor Drive runs with maximum torque, less noise and maximum efficiency when the higher level of multi-level inverter output is fed to it).

Cite this paper

HaiderAli,Mohamed Z. H.Qawaqzeh,MuhammadAbbas,Takialddin AlSmadi, (2015) Implementation & Comparative Analysis of 10, 18 & 24 Level Diode Clamped Inverters Using “Trust Region Dog Leg” Method. Circuits and Systems,06,70-80. doi: 10.4236/cs.2015.63008

References

- 1. Peddapeli, S.K. (2014) Recent Advances in Pulse Width Modulation Techniques and Multilevel Inverters. International Journal of Electrical, Electronic Science and Engineering, 8, 568-576.

- 2. Hussein, H. (2014) Harmonics Elimination PWM (HEPWM). International Journal of Engineering Research and General Science, 2, 172-181.

- 3. Satyanarayana, G.V.R. and Ganesh, S.N.V. (2010) Cascaded 5-Level Inverter Type DSTATCOM for Power Quality Improvement. 2010 IEEE Students’ Technology Symposium (TechSym), Kharagpur, 3-4 April 2010, 166-170.

http://dx.doi.org/10.1109/TECHSYM.2010.5469168 - 4. Shukla, A., Ghosh, A. and Joshi, A. (2010) Flying-Capacitor-Based Chopper Circuit for DC Capacitor Voltage Balancing in Diode-Clamped Multilevel Inverter. IEEE Transactions on Industrial Electronics, 57, 2249-2261.

http://dx.doi.org/10.1109/TIE.2009.2029527 - 5. Boora, A.A., Nami, A., Zare, F., Ghosh, A. and Blaabjerg, F. (2010) Voltage-Sharing Converter to Supply Single-Phase Asymmetrical Four-Level Diode-Clamped Inverter with High Power Factor Loads. IEEE Transactions on Power Electronics, 25, 2507-2520.

http://dx.doi.org/10.1109/TPEL.2010.2046651 - 6. Cavalcanti, M.C., Farias, A.M., Oliveira, K.C., Neves, F.A. and Afonso, J.L. (2012) Eliminating Leakage Currents in Neutral Point Clamped Inverters for Photovoltaic Systems. IEEE Transactions on Industrial Electronics, 59, 435-443.

http://dx.doi.org/10.1109/TIE.2011.2138671 - 7. Li, J., Liu, J., Boroyevich, D., Mattavelli, P. and Xue, Y. (2011) Comparative Analysis of Three-Level Diode Neural-Point-Clamped and Active Neural-Point-Clamped Zero-Current-Transition Inverters. 2011 IEEE 8th International Conference on Power Electronics and ECCE Asia (ICPE & ECCE), Jeju, 30 May-3 June 2011, 2290-2295.

http://dx.doi.org/10.1109/ICPE.2011.5944469 - 8. Du, Z., Tolbert, L.M., Ozpineci, B. and Chiasson, J.N. (2009) Fundamental Frequency Switching Strategies of a Seven-Level Hybrid Cascaded H-Bridge Multilevel Inverter. IEEE Transactions on Power Electronics, 24, 25-33.

http://dx.doi.org/10.1109/TPEL.2008.2006678 - 9. Khazraei, M., Sepahvand, H., Corzine, K.A. and Ferdowsi, M. (2012) Active Capacitor Voltage Balancing in Single-Phase Flying-Capacitor Multilevel Power Converters. IEEE Transactions on Industrial Electronics, 59, 769-778.

http://dx.doi.org/10.1109/TIE.2011.2157290 - 10. Chaturvedi, P.K., Jain, S. and Agarwal, P. (2011) Reduced Switching Loss Pulse Width Modulation Technique for Three-Level Diode Clamped Inverter. IET Power Electronics, 4, 393-399.

http://dx.doi.org/10.1049/iet-pel.2010.0311 - 11. Massoud, A.M., Ahmed, S., Enjeti, P.N. and Williams, B.W. (2010) Evaluation of a Multilevel Cascaded-Type Dynamic Voltage Restorer Employing Discontinuous Space Vector Modulation. IEEE Transactions on Industrial Electronics, 57, 2398-2410.

http://dx.doi.org/10.1109/TIE.2010.2041732 - 12. Taghizadeh, H. and Hagh, M.T. (2010) Harmonic Elimination of Cascade Multilevel Inverters with Nonequal DC Sources Using Particle Swarm Optimization. IEEE Transactions on Industrial Electronics, 57, 3678-3684.

http://dx.doi.org/10.1109/TIE.2010.2041736 - 13. Al Smadi, T.A. (2013) Design and Implementation of Double Base Integer Encoder of Term Metrical to Direct Binary. Journal of Signal and Information Processing, 4, 370.

http://www.scirp.org/journal/PaperInformation.aspx?paperID=38910

http://dx.doi.org/10.4236/jsip.2013.44047