A Timing Skew Calibration Scheme in Time-Interleaved ADC

Open Access JCC

among channels is assumed to satisfy Gauss distribution

with a sta n da rd devia t ion of 0.01Ts.

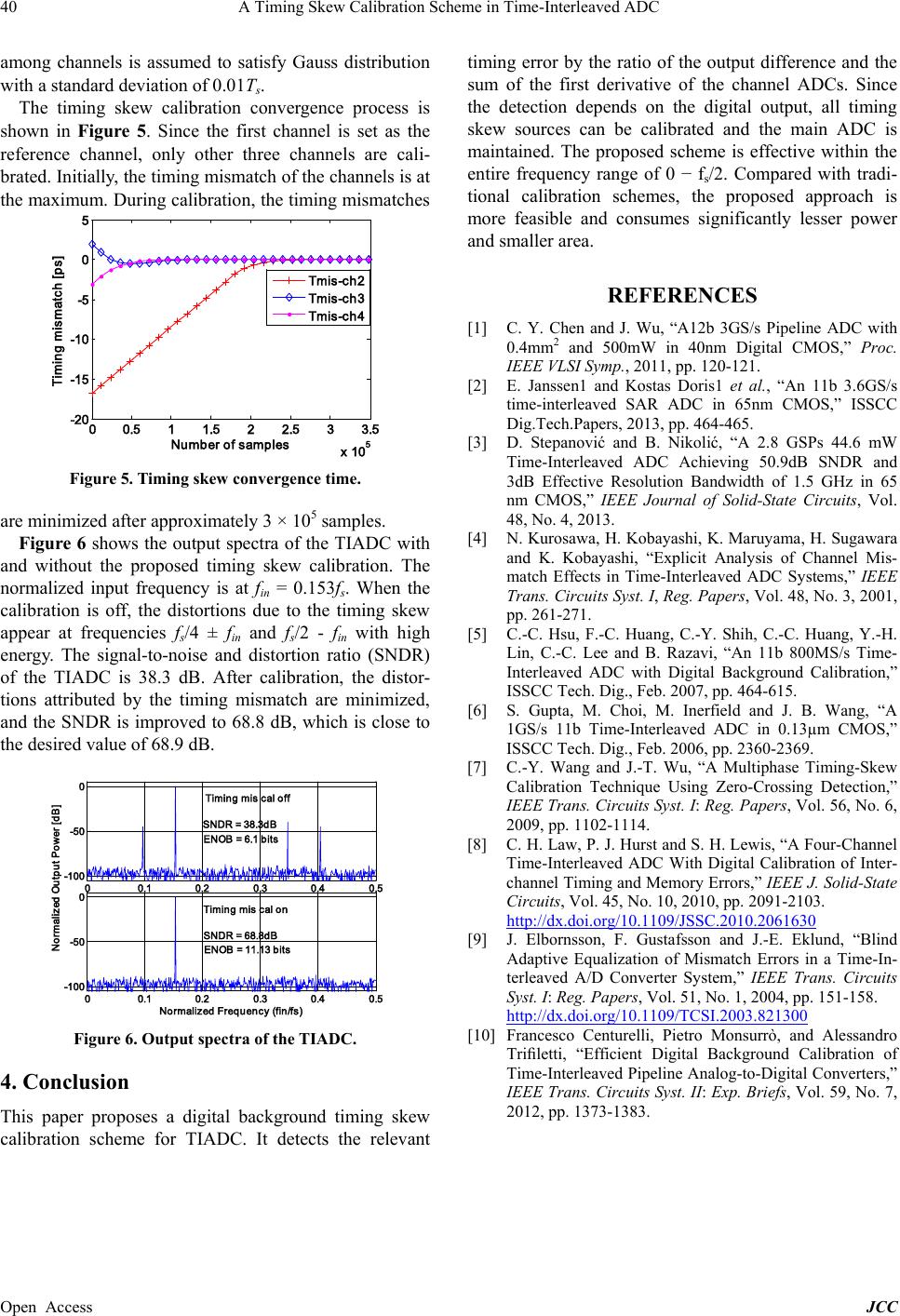

The timing skew calibration convergence process is

shown in Figure 5. Since the first channel is set as the

reference channel, only other three channels are cali-

brated. Initially, the timing mismatch of the channels is at

the maximum. During calibration , the timing mismatches

Figure 5. Timing skew convergence time.

are minimized after approximately 3 × 105 samp le s.

Figure 6 shows the output spectra of the TIADC with

and without the proposed timing skew calibration. The

normalized input frequency is at fin = 0.153fs. When the

calibration is off, the distortions due to the timing skew

appear at frequencies fs/4 ± fin and fs/2 - fin with high

energy. The signal-to-noise and distortion ratio (SNDR)

of the TIADC is 38.3 dB. After calibration, the distor-

tions attributed by the timing mismatch are minimized,

and the SNDR is improved to 68.8 dB, which is close to

the desired value of 68.9 dB.

Figure 6. Output spectra of the TIADC.

4. Conclusion

This paper proposes a digital background timing skew

calibration scheme for TIADC. It detects the relevant

timing error by the ratio of the output difference and the

sum of the first derivative of the channel ADCs. Since

the detection depends on the digital output, all timing

skew sources can be calibrated and the main ADC is

maintained. The proposed scheme is effective within the

entire frequency range of 0 − fs/2. Compared with tradi-

tional calibration schemes, the proposed approach is

more feasible and consumes significantly lesser power

and smaller area.

REFERENCES

[1] C. Y. Chen and J. Wu, “A12b 3GS/s Pipeline ADC with

0.4mm2 and 500mW in 40nm Digital CMOS,” Proc.

IEEE VLSI Symp., 2011, pp. 120-121.

[2] E. Janssen1 and Kostas Doris1 et al., “An 11b 3.6GS/s

time-interleaved SAR ADC in 65nm CMOS,” ISSCC

Dig.Tech.Papers, 2013, pp. 464-465.

[3] D. Stepanović and B. Nikolić, “A 2.8 GSPs 44.6 mW

Time-Interleaved ADC Achieving 50.9dB SNDR and

3dB Effective Resolution Bandwidth of 1.5 GHz in 65

nm CMOS,” IEEE Journal of Solid-State Circuits, Vol.

48, No. 4, 2013.

[4] N. Kuros awa, H. Kobayashi, K. Maruyama, H. Sugawara

and K. Kobayashi, “Explicit Analysis of Channel Mis-

match Effects in Time-Interleaved ADC Systems,” IEEE

Trans. Circuit s Syst. I, Reg. Papers, Vol. 48, No. 3, 2001,

pp. 261-271.

[5] C.-C. Hsu, F.-C. Huang, C.-Y. Shih, C.-C. Huang, Y.-H.

Lin, C.-C. Lee and B. Razavi, “An 11b 800MS/s Time-

Interleaved ADC with Digital Background Calibration,”

ISSCC Tech. Dig., Feb. 2007, pp. 464-615.

[6] S. Gupta, M. Choi, M. Inerfield and J. B. Wang, “A

1GS/s 11b Time-Interleaved ADC in 0.13µm CMOS,”

ISSCC Tech. Dig., Feb. 2006, pp. 2360-2369.

[7] C.-Y. Wang and J.-T. Wu, “A Multiphase Timing-Skew

Calibration Technique Using Zero-Crossing Detection,”

IEEE Trans. Circuits Syst. I: Reg. Papers, Vol. 56, No. 6,

2009, pp. 1102-1114.

[8] C. H. Law, P. J. Hurst and S. H. Le wis, “A Four-Channel

Time-Interleaved ADC With Digital Calibration of Inter-

channel Timing and Memory Errors,” IEEE J. Solid-State

Circuits, Vol. 45, No. 10, 2010, pp. 2091-2103.

http://dx.doi.org/10.1109/JSSC.2010.2061630

[9] J. Elbornsson, F. Gustafsson and J.-E. Eklund, “Blind

Adaptive Equalization of Mismatch Errors in a Time-In-

terleaved A/D Converter System,” IEEE Trans. Circuits

Syst. I: Reg. Papers, Vol. 51, No. 1, 2004, pp. 151-158.

http://dx.doi.org/10.1109/TCSI.2003.821300

[10] Francesco Centurelli, Pietro Monsurrò, and Alessandro

Trifiletti, “Efficient Digital Background Calibration of

Time-Interleaved Pipeline Analog-to-Digital Converters,”

IEEE Trans. Circuits Syst. II: Exp. Briefs, Vol. 59, No. 7,

2012, pp. 1373-1383.

00.5 11.5 22.5 33.5

x 10

5

-20

-15

-10

-5

0

5

N um ber of sampl es

T im ing m isma tc h [ ps]

Tmis-ch2

Tmis-ch3

Tmis-ch4

00.1 0.2 0.3 0.4 0.5

-100

-50

0Timing mis cal off

SNDR = 38.3dB

ENOB = 6.1 bits

00.1 0.2 0.3 0.4 0.5

-100

-50

0

Nor m ali zed Fre quency (fi n/fs)

Nor m alized Output Power [dB]

Timing mis cal on

SNDR = 68.8dB

ENOB = 11.13 bits