C. Q. SHI ET AL. 9

Figure 8. Tuning curves of the ILFD.

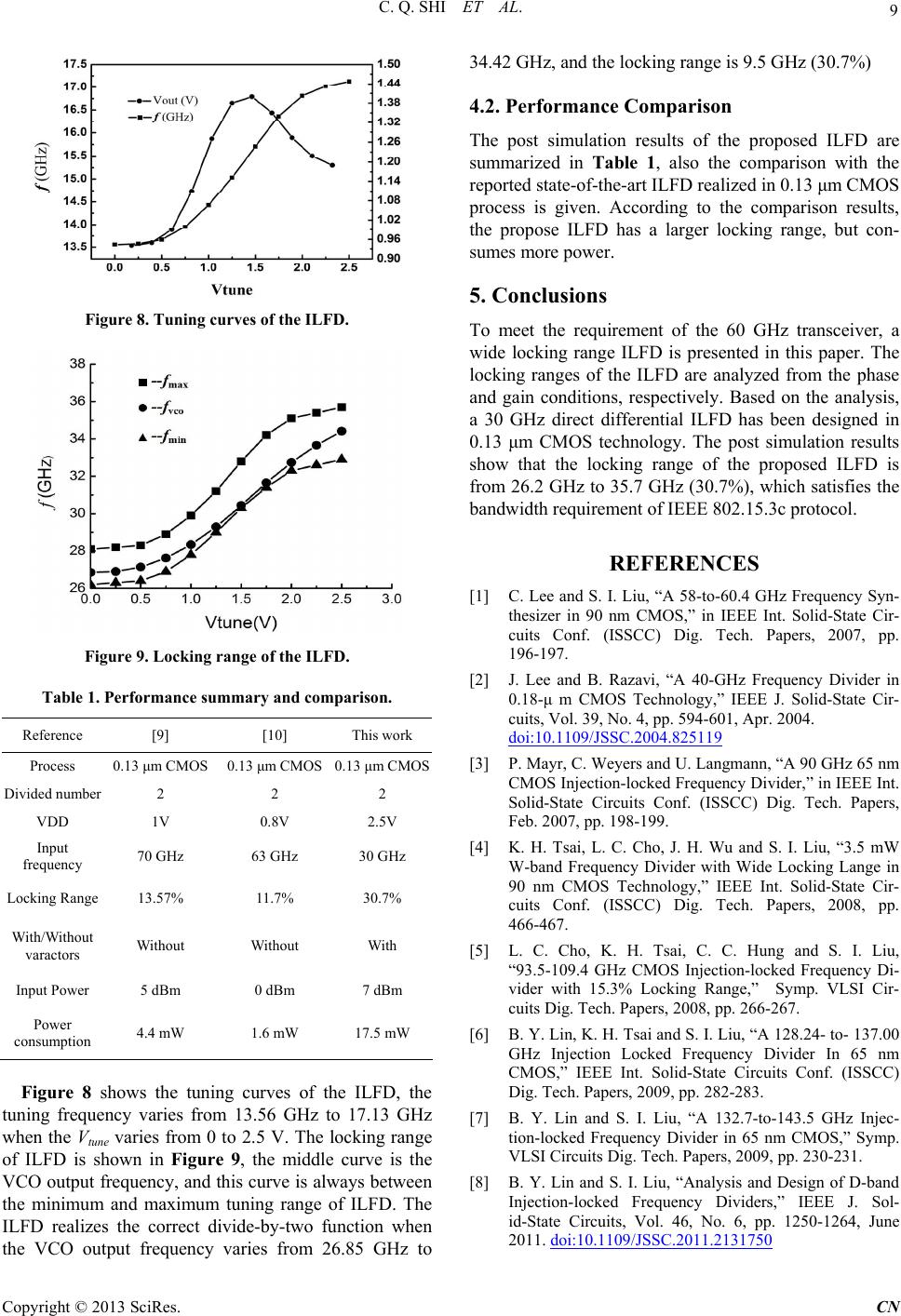

Figure 9. Locking range of the ILFD.

Table 1. Performance summary and comparison.

Reference [9] [10] This work

Process 0.13 μm CMOS 0.13 μm CMOS 0.13 μm CMOS

Divided number 2 2 2

VDD 1V 0.8V 2.5V

Input

frequency 70 GHz 63 GHz 30 GHz

Locking Range 13.57% 11.7% 30.7%

With/Without

varactors Without Without With

Input Power5 dBm 0 dBm 7 dBm

Power

consumption 4.4 mW 1.6 mW 17.5 mW

Figure 8 shows the tuning curves of the ILFD, the

tuning frequency varies from 13.56 GHz to 17.13 GHz

when the Vtune varies from 0 to 2.5 V. The locking range

of ILFD is shown in Figure 9, the middle curve is the

VCO output frequency, and this curve is always between

the minimum and maximum tuning range of ILFD. The

ILFD realizes the correct divide-by-two function when

the VCO output frequency varies from 26.85 GHz to

34.42 GHz, and the locking range is 9.5 GHz (30.7%)

4.2. Performance Comparison

The post simulation results of the proposed ILFD are

summarized in Table 1, also the comparison with the

reported state-of-the-art ILFD realized in 0.13 μm CMOS

process is given. According to the comparison results,

the propose ILFD has a larger locking range, but con-

sumes more power.

5. Conclusions

To meet the requirement of the 60 GHz transceiver, a

wide locking range ILFD is presented in this paper. The

locking ranges of the ILFD are analyzed from the phase

and gain conditions, respectively. Based on the analysis,

a 30 GHz direct differential ILFD has been designed in

0.13 μm CMOS technology. The post simulation results

show that the locking range of the proposed ILFD is

from 26.2 GHz to 35.7 GHz (30.7%), which satisfies the

bandwidth requirement of IEEE 802.15.3c protocol.

REFERENCES

[1] C. Lee and S. I. Liu, “A 58-to-60.4 GHz Frequency Syn-

thesizer in 90 nm CMOS,” in IEEE Int. Solid-State Cir-

cuits Conf. (ISSCC) Dig. Tech. Papers, 2007, pp.

196-197.

[2] J. Lee and B. Razavi, “A 40-GHz Frequency Divider in

0.18-μ m CMOS Technology,” IEEE J. Solid-State Cir-

cuits, Vol. 39, No. 4, pp. 594-601, Apr. 2004.

doi:10.1109/JSSC.2004.825119

[3] P. Mayr, C. Weyers and U. Langmann, “A 90 GHz 65 nm

CMOS Injection-locked Frequency Divider,” in IEEE Int.

Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers,

Feb. 2007, pp. 198-199.

[4] K. H. Tsai, L. C. Cho, J. H. Wu and S. I. Liu, “3.5 mW

W-band Frequency Divider with Wide Locking Lange in

90 nm CMOS Technology,” IEEE Int. Solid-State Cir-

cuits Conf. (ISSCC) Dig. Tech. Papers, 2008, pp.

466-467.

[5] L. C. Cho, K. H. Tsai, C. C. Hung and S. I. Liu,

“93.5-109.4 GHz CMOS Injection-locked Frequency Di-

vider with 15.3% Locking Range,” Symp. VLSI Cir-

cuits Dig. Tech. Papers, 2008, pp. 266-267.

[6] B. Y. Lin, K. H. Tsai and S. I. Liu, “A 128.24- to- 137.00

GHz Injection Locked Frequency Divider In 65 nm

CMOS,” IEEE Int. Solid-State Circuits Conf. (ISSCC)

Dig. Tech. Papers, 2009, pp. 282-283.

[7] B. Y. Lin and S. I. Liu, “A 132.7-to-143.5 GHz Injec-

tion-locked Frequency Divider in 65 nm CMOS,” Symp.

VLSI Circuits Dig. Tech. Papers, 2009, pp. 230-231.

[8] B. Y. Lin and S. I. Liu, “Analysis and Design of D-band

Injection-locked Frequency Dividers,” IEEE J. Sol-

id-State Circuits, Vol. 46, No. 6, pp. 1250-1264, June

2011. doi:10.1109/JSSC.2011.2131750

Copyright © 2013 SciRes. CN