Y. S. YUAN, Q. F. WU

130

Figure 6. ugs1 ,uds1 and ids1waveforms w ith 250 W load.

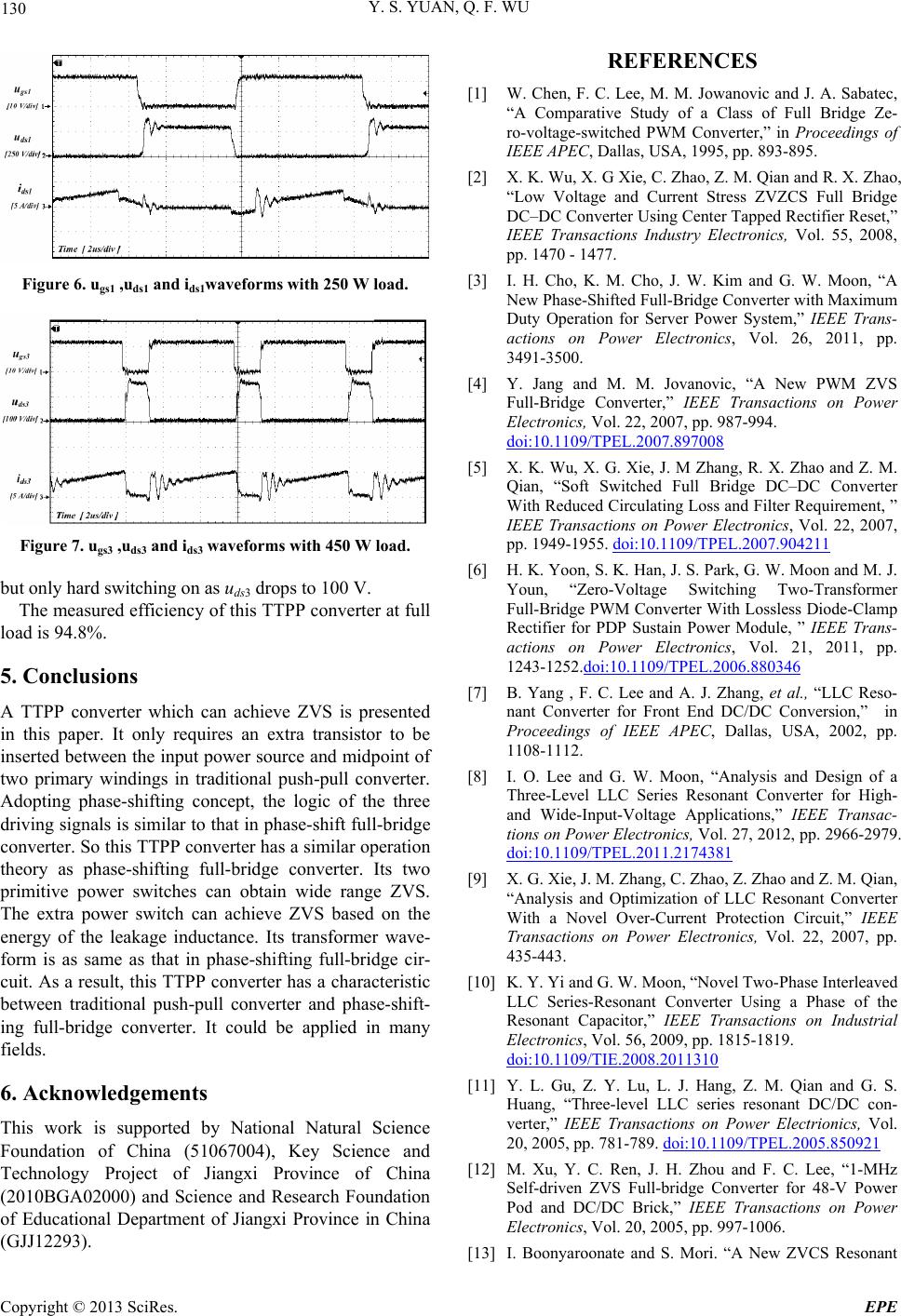

Figure 7. ugs3 ,uds3 and ids3 waveforms with 450 W load.

but only hard switching on as uds3 drops to 100 V.

The measured efficiency of this TTPP converter at full

load is 94.8%.

5. Conclusions

A TTPP converter which can achieve ZVS is presented

in this paper. It only requires an extra transistor to be

inserted between the input power source and midpoint of

two primary windings in traditional push-pull converter.

Adopting phase-shifting concept, the logic of the three

driving signals is similar to that in phase-shift full-bridge

converter. So this TTPP converter has a similar operation

theory as phase-shifting full-bridge converter. Its two

primitive power switches can obtain wide range ZVS.

The extra power switch can achieve ZVS based on the

energy of the leakage inductance. Its transformer wave-

form is as same as that in phase-shifting full-bridge cir-

cuit. As a result, this TTPP converter has a characteristic

between traditional push-pull converter and phase-shift-

ing full-bridge converter. It could be applied in many

fields.

6. Acknowledgements

This work is supported by National Natural Science

Foundation of China (51067004), Key Science and

Technology Project of Jiangxi Province of China

(2010BGA02000) and Science and Research Foundation

of Educational Department of Jiangxi Province in China

(GJJ12293).

REFERENCES

[1] W. Chen, F. C. Lee, M. M. Jowanovic and J. A. Sabatec,

“A Comparative Study of a Class of Full Bridge Ze-

ro-voltage-switched PWM Converter,” in Proceedings of

IEEE APEC, Dallas, USA, 1995, pp. 893-895.

[2] X. K. Wu, X. G Xie, C. Zhao, Z. M. Qian and R. X. Zhao,

“Low Voltage and Current Stress ZVZCS Full Bridge

DC–DC Converter Using Center Tapped Rectifier Reset,”

IEEE Transactions Industry Electronics, Vol. 55, 2008,

pp. 1470 - 1477.

[3] I. H. Cho, K. M. Cho, J. W. Kim and G. W. Moon, “A

New Phase-Shifted Full-Bridge Converter with Maximum

Duty Operation for Server Power System,” IEEE Trans-

actions on Power Electronics, Vol. 26, 2011, pp.

3491-3500.

[4] Y. Jang and M. M. Jovanovic, “A New PWM ZVS

Full-Bridge Converter,” IEEE Transactions on Power

Electronics, Vol. 22, 2007, pp. 987-994.

doi:10.1109/TPEL.2007.897008

[5] X. K. Wu, X. G. Xie, J. M Zhang, R. X. Zhao and Z. M.

Qian, “Soft Switched Full Bridge DC–DC Converter

With Reduced Circulating Loss and Filter Requirement, ”

IEEE Transactions on Power Electronics, Vol. 22, 2007,

pp. 1949-1955. doi:10.1109/TPEL.2007.904211

[6] H. K. Yoon, S. K. Han, J. S. Park, G. W. Moon and M. J.

Youn, “Zero-Voltage Switching Two-Transformer

Full-Bridge PWM Converter With Lossless Diode-Clamp

Rectifier for PDP Sustain Power Module, ” IEEE Trans-

actions on Power Electronics, Vol. 21, 2011, pp.

1243-1252.doi:10.1109/TPEL.2006.880346

[7] B. Yang , F. C. Lee and A. J. Zhang, et al., “LLC Reso-

nant Converter for Front End DC/DC Conversion,” in

Proceedings of IEEE APEC, Dallas, USA, 2002, pp.

1108-1112.

[8] I. O. Lee and G. W. Moon, “Analysis and Design of a

Three-Level LLC Series Resonant Converter for High-

and Wide-Input-Voltage Applications,” IEEE Transac-

tions on Power Electronics, Vol. 27, 2012, pp. 2966-2979.

doi:10.1109/TPEL.2011.2174381

[9] X. G. Xie, J. M. Zhang, C. Zhao, Z. Zhao and Z. M. Qian,

“Analysis and Optimization of LLC Resonant Converter

With a Novel Over-Current Protection Circuit,” IEEE

Transactions on Power Electronics, Vol. 22, 2007, pp.

435-443.

[10] K. Y. Yi and G. W. Moon, “Novel Two-Phase Interleaved

LLC Series-Resonant Converter Using a Phase of the

Resonant Capacitor,” IEEE Transactions on Industrial

Electronics, Vol. 56, 2009, pp. 1815-1819.

doi:10.1109/TIE.2008.2011310

[11] Y. L. Gu, Z. Y. Lu, L. J. Hang, Z. M. Qian and G. S.

Huang, “Three-level LLC series resonant DC/DC con-

verter,” IEEE Transactions on Power Electrionics, Vol.

20, 2005, pp. 781-789. doi:10.1109/TPEL.2005.850921

[12] M. Xu, Y. C. Ren, J. H. Zhou and F. C. Lee, “1-MHz

Self-driven ZVS Full-bridge Converter for 48-V Power

Pod and DC/DC Brick,” IEEE Transactions on Power

Electronics, Vol. 20, 2005, pp. 997-1006.

[13] I. Boonyaroonate and S. Mori. “A New ZVCS Resonant

Copyright © 2013 SciRes. EPE