C.-H. HO, J.-H. HO

388

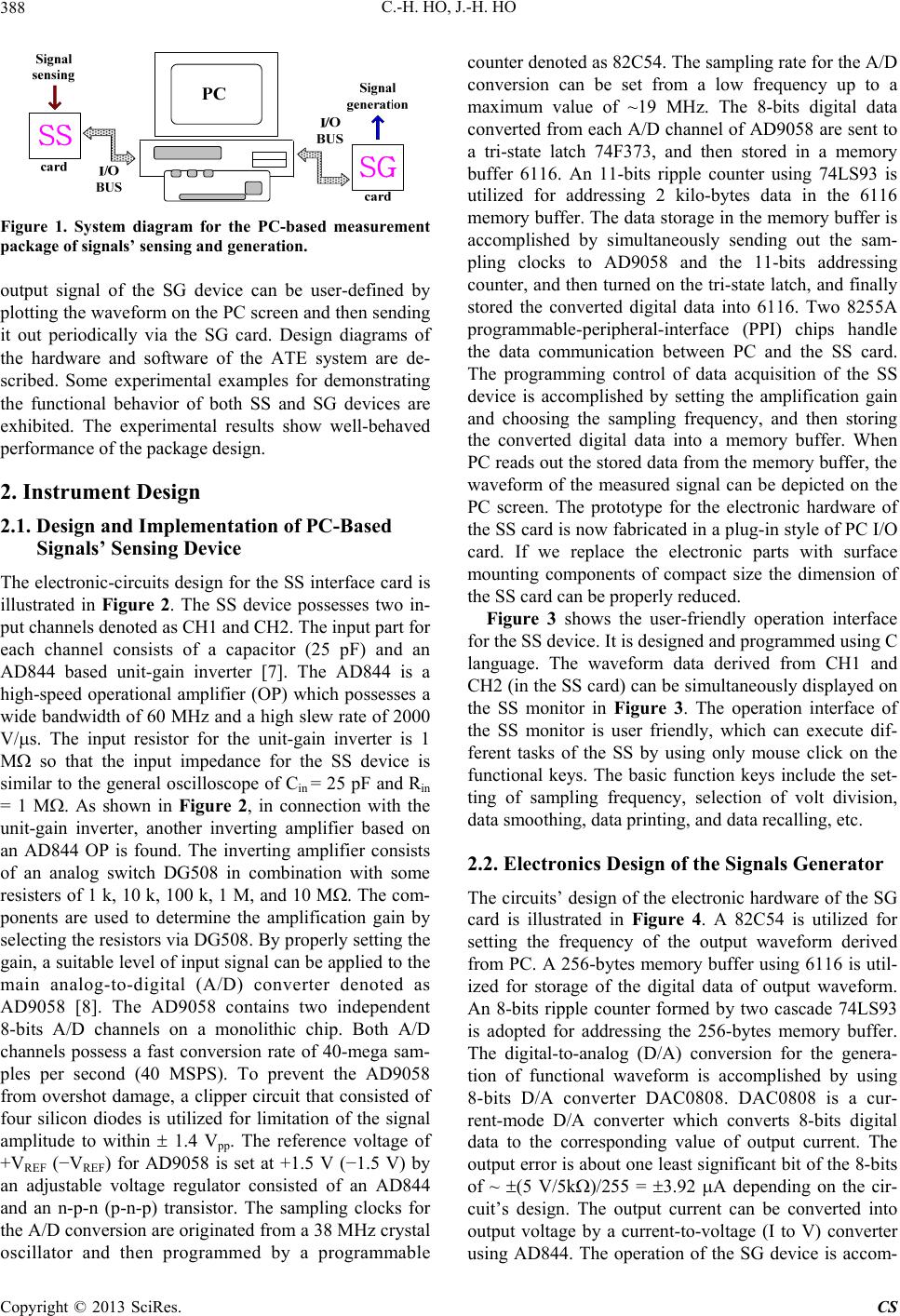

Figure 1. System diagram for the PC-based measurement

package of signals’ sensing and generation.

output signal of the SG device can be user-defined by

plotting the waveform on the PC screen and then sending

it out periodically via the SG card. Design diagrams of

the hardware and software of the ATE system are de-

scribed. Some experimental examples for demonstrating

the functional behavior of both SS and SG devices are

exhibited. The experimental results show well-behaved

performance of the package design.

2. Instrument Design

2.1. Design and Implementation of PC-Based

Signals’ Sensing Device

The electronic-circuits design for the SS interface card is

illustrated in Figure 2. The SS device possesses two in-

put channels denoted as CH1 and CH2. The input part for

each channel consists of a capacitor (25 pF) and an

AD844 based unit-gain inverter [7]. The AD844 is a

high-speed operational amplifier (OP) which possesses a

wide bandwidth of 60 MHz and a high slew rate of 2000

V/s. The input resistor for the unit-gain inverter is 1

M so that the input impedance for the SS device is

similar to the general oscilloscope of Cin = 25 pF and Rin

= 1 M. As shown in Figure 2, in connection with the

unit-gain inverter, another inverting amplifier based on

an AD844 OP is found. The inverting amplifier consists

of an analog switch DG508 in combination with some

resisters of 1 k, 10 k, 100 k, 1 M, and 10 M. The com-

ponents are used to determine the amplification gain by

selecting the resistors via DG508. By properly setting the

gain, a suitable level of input signal can be applied to the

main analog-to-digital (A/D) converter denoted as

AD9058 [8]. The AD9058 contains two independent

8-bits A/D channels on a monolithic chip. Both A/D

channels possess a fast conversion rate of 40-mega sam-

ples per second (40 MSPS). To prevent the AD9058

from overshot damage, a clipper circuit that consisted of

four silicon diodes is utilized for limitation of the signal

amplitude to within 1.4 Vpp. The reference voltage of

+VREF (−VREF) for AD9058 is set at +1.5 V (−1.5 V) by

an adjustable voltage regulator consisted of an AD844

and an n-p-n (p-n-p) transistor. The sampling clocks for

the A/D conversion are originated from a 38 MHz crystal

oscillator and then programmed by a programmable

counter denoted as 82C54. The sampling rate for the A/D

conversion can be set from a low frequency up to a

maximum value of ~19 MHz. The 8-bits digital data

converted from each A/D channel of AD9058 are sent to

a tri-state latch 74F373, and then stored in a memory

buffer 6116. An 11-bits ripple counter using 74LS93 is

utilized for addressing 2 kilo-bytes data in the 6116

memory buffer. The data storage in the memory buffer is

accomplished by simultaneously sending out the sam-

pling clocks to AD9058 and the 11-bits addressing

counter, and then turned on the tri-state latch, and finally

stored the converted digital data into 6116. Two 8255A

programmable-peripheral-interface (PPI) chips handle

the data communication between PC and the SS card.

The programming control of data acquisition of the SS

device is accomplished by setting the amplification gain

and choosing the sampling frequency, and then storing

the converted digital data into a memory buffer. When

PC reads out the stored data from the memory buffer, the

waveform of the measured signal can be depicted on the

PC screen. The prototype for the electronic hardware of

the SS card is now fabricated in a plug-in style of PC I/O

card. If we replace the electronic parts with surface

mounting components of compact size the dimension of

the SS card can be properly reduced.

Figure 3 shows the user-friendly operation interface

for the SS device. It is designed and programmed using C

language. The waveform data derived from CH1 and

CH2 (in the SS card) can be simultaneously displayed on

the SS monitor in Figure 3. The operation interface of

the SS monitor is user friendly, which can execute dif-

ferent tasks of the SS by using only mouse click on the

functional keys. The basic function keys include the set-

ting of sampling frequency, selection of volt division,

data smoothing, data printing, and data recalling, etc.

2.2. Electronics Design of the Signals Generator

The circuits’ design of the electronic hardware of the SG

card is illustrated in Figure 4. A 82C54 is utilized for

setting the frequency of the output waveform derived

from PC. A 256-bytes memory buffer using 6116 is util-

ized for storage of the digital data of output waveform.

An 8-bits ripple counter formed by two cascade 74LS93

is adopted for addressing the 256-bytes memory buffer.

The digital-to-analog (D/A) conversion for the genera-

tion of functional waveform is accomplished by using

8-bits D/A converter DAC0808. DAC0808 is a cur-

rent-mode D/A converter which converts 8-bits digital

data to the corresponding value of output current. The

output error is about one least significant bit of the 8-bits

of ~ (5 V/5k)/255 = 3.92 A depending on the cir-

cuit’s design. The output current can be converted into

output voltage by a current-to-voltage (I to V) converter

using AD844. The operation of the SG device is accom-

Copyright © 2013 SciRes. CS