F. TALEBI ET AL.

314

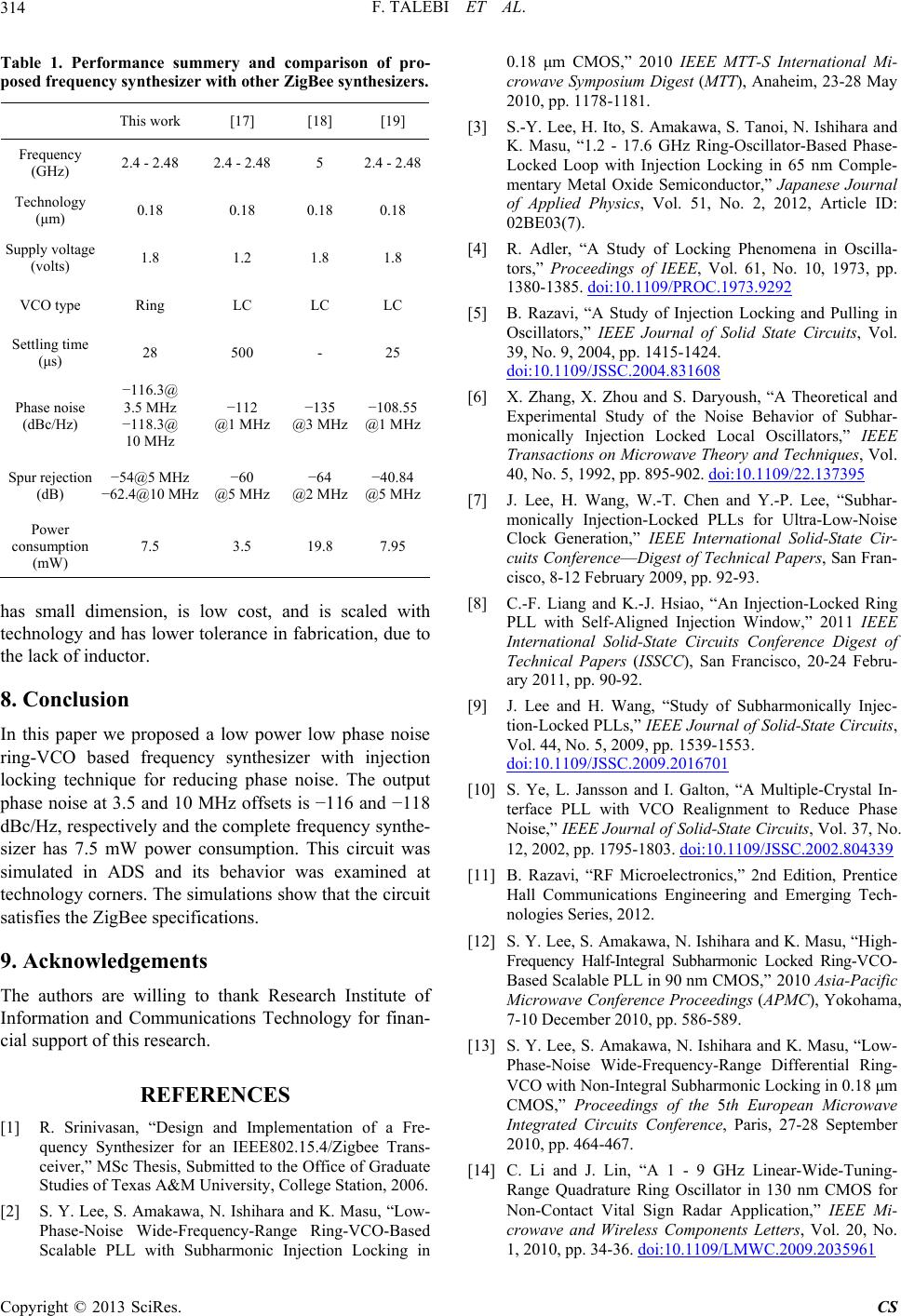

Table 1. Performance summery and comparison of pro-

posed frequency sy nthe sizer with other ZigBee synthesizers.

This work [17] [18] [19]

Frequency

(GHz) 2.4 - 2.48 2.4 - 2.48 5 2.4 - 2.48

Technology

(μm) 0.18 0.18 0.18 0.18

Supply voltage

(volts) 1.8 1.2 1.8 1.8

VCO type Ring LC LC LC

Settling time

(μs) 28 500 - 25

Phase noise

(dBc/Hz)

−116.3@

3.5 MHz

−118.3@

10 MHz

−112

@1 MHz

−135

@3 MHz

−108.55

@1 MHz

Spur rejection

(dB)

−54@5 MHz

−62.4@10 MHz

−60

@5 MHz

−64

@2 MHz

−40.84

@5 MHz

Power

consumption

(mW)

7.5 3.5 19.8 7.95

has small dimension, is low cost, and is scaled with

technology and has lower tolerance in fabrication, due to

the lack of inductor.

8. Conclusion

In this paper we proposed a low power low phase noise

ring-VCO based frequency synthesizer with injection

locking technique for reducing phase noise. The output

phase noise at 3.5 and 10 MHz offsets is −116 and −118

dBc/Hz, respectively and the complete frequency synthe-

sizer has 7.5 mW power consumption. This circuit was

simulated in ADS and its behavior was examined at

technology corners. The simulations show that the circuit

satisfies the ZigBee specifications.

9. Acknowledgements

The authors are willing to thank Research Institute of

Information and Communications Technology for finan-

cial support of this research.

REFERENCES

[1] R. Srinivasan, “Design and Implementation of a Fre-

quency Synthesizer for an IEEE802.15.4/Zigbee Trans-

ceiver,” MSc Thesis, Submitted to the Office of Graduate

Studies of Texas A&M University, College Station, 2006.

[2] S. Y. Lee, S. Amakawa, N. Ishihara and K. Masu, “Low-

Phase-Noise Wide-Frequency-Range Ring-VCO-Based

Scalable PLL with Subharmonic Injection Locking in

0.18 μm CMOS,” 2010 IEEE MTT-S International Mi-

crowave Symposium Digest (MTT), Anaheim, 23-28 May

2010, pp. 1178-1181.

[3] S.-Y. Lee, H. Ito, S. Amakawa, S. Tanoi, N. Ishihara and

K. Masu, “1.2 - 17.6 GHz Ring-Oscillator-Based Phase-

Locked Loop with Injection Locking in 65 nm Comple-

mentary Metal Oxide Semiconductor,” Japanese Journal

of Applied Physics, Vol. 51, No. 2, 2012, Article ID:

02BE03(7).

[4] R. Adler, “A Study of Locking Phenomena in Oscilla-

tors,” Proceedings of IEEE, Vol. 61, No. 10, 1973, pp.

1380-1385. doi:10.1109/PROC.1973.9292

[5] B. Razavi, “A Study of Injection Locking and Pulling in

Oscillators,” IEEE Journal of Solid State Circuits, Vol.

39, No. 9, 2004, pp. 1415-1424.

doi:10.1109/JSSC.2004.831608

[6] X. Zhang, X. Zhou and S. Daryoush, “A Theoretical and

Experimental Study of the Noise Behavior of Subhar-

monically Injection Locked Local Oscillators,” IEEE

Transactions on Microwave Theory and Techniques, Vol.

40, No. 5, 1992, pp. 895-902. doi:10.1109/22.137395

[7] J. Lee, H. Wang, W.-T. Chen and Y.-P. Lee, “Subhar-

monically Injection-Locked PLLs for Ultra-Low-Noise

Clock Generation,” IEEE International Solid-State Cir-

cuits Conference—Digest of Technical Papers, San Fran-

cisco, 8-12 February 2009, pp. 92-93.

[8] C.-F. Liang and K.-J. Hsiao, “An Injection-Locked Ring

PLL with Self-Aligned Injection Window,” 2011 IEEE

International Solid-State Circuits Conference Digest of

Technical Papers (ISSCC), San Francisco, 20-24 Febru-

ary 2011, pp. 90-92.

[9] J. Lee and H. Wang, “Study of Subharmonically Injec-

tion-Locked PLLs,” IEEE Journal of Solid-State Circuits,

Vol. 44, No. 5, 2009, pp. 1539-1553.

doi:10.1109/JSSC.2009.2016701

[10] S. Ye, L. Jansson and I. Galton, “A Multiple-Crystal In-

terface PLL with VCO Realignment to Reduce Phase

Noise,” IEEE Journal of Solid-State Circuits, Vol. 37, No.

12, 2002, pp. 1795-1803. doi:10.1109/JSSC.2002.804339

[11] B. Razavi, “RF Microelectronics,” 2nd Edition, Prentice

Hall Communications Engineering and Emerging Tech-

nologies Series, 2012.

[12] S. Y. Lee, S. Amakawa, N. Ishihara and K. Masu, “High-

Frequency Half-Integral Subharmonic Locked Ring-VCO-

Based Scalable PLL in 90 nm CMOS,” 2010 Asia-Pacific

Microwave Conference Proceedings (APMC), Yokohama,

7-10 December 2010, pp. 586-589.

[13] S. Y. Lee, S. Amakawa, N. Ishihara and K. Masu, “Low-

Phase-Noise Wide-Frequency-Range Differential Ring-

VCO with Non-Integral Subharmonic Locking in 0.18 μm

CMOS,” Proceedings of the 5th European Microwave

Integrated Circuits Conference, Paris, 27-28 September

2010, pp. 464-467.

[14] C. Li and J. Lin, “A 1 - 9 GHz Linear-Wide-Tuning-

Range Quadrature Ring Oscillator in 130 nm CMOS for

Non-Contact Vital Sign Radar Application,” IEEE Mi-

crowave and Wireless Components Letters, Vol. 20, No.

1, 2010, pp. 34-36. doi:10.1109/LMWC.2009.2035961

Copyright © 2013 SciRes. CS