O. S. AHMED ET AL. 279

Table 3. All transitions between initial LPs and merged

LPs.

LP1,0 LP2,0 LP3,0

LP1 9 0 6

LP2 3 3 0

L3 P3 3 0

LP4 0 9 0

LP5 0 0 6

Ta. Node trans with dit delay m

Nonsitions E

G H

ble 4sitionfferenodels.

de tra

F

Zero-delay model 96 120 110 126

Unit-delay model 96 144 152 144

Tesit chterist

Circuit Inputs

Nodes L

count

Crit

path Me

saving

Table 5.t circuaracics.

Ps ical

gates

mory

ISCAS85-C17 5 6 10 1.7 3

7483 9 36 162 4 1.6

74157 10 15 34 4 15.5

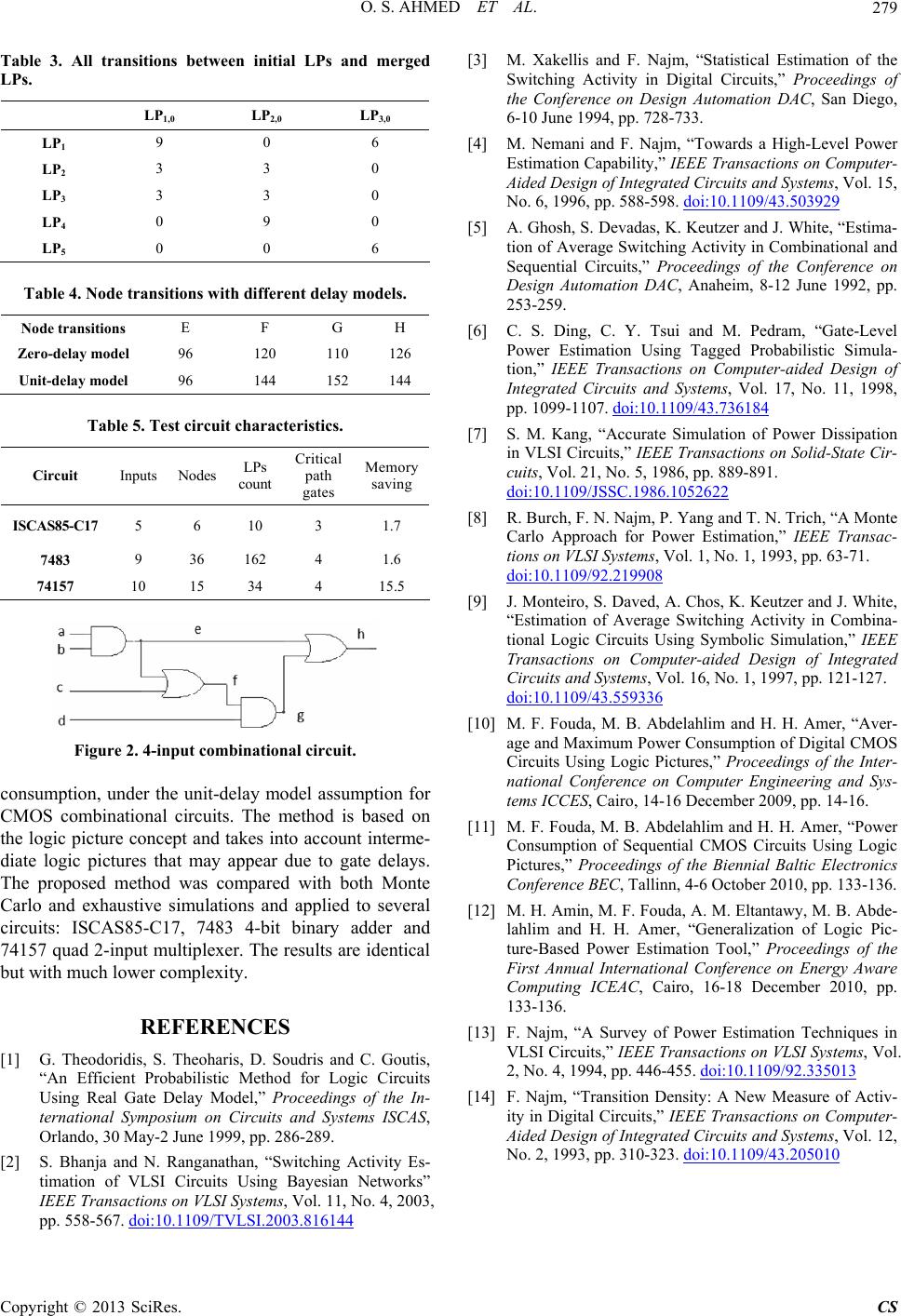

Figure 2. 4-input combinational circuit.

consumption, under the unit-delay model assump

CMOS coba

e logic interme-

. Soudris and C. Goutis,

“An Efficient Probabilistic Method for Logic Circuits

Using Real Geedings of the In-

ternational Syd Systems ISCAS

4

tion f

sed on

or

mbinational circuits. The method is

picture concept and takes into account th

diate logic pictures that may appear due to gate delays.

The proposed method was compared with both Monte

Carlo and exhaustive simulations and applied to several

circuits: ISCAS85-C17, 7483 4-bit binary adder and

74157 quad 2-inpu t multiplexer. Th e results are identical

but with much lower complexity.

REFERENCES

[1] G. Theodoridis, S. Theoharis, D

ate Delay Model,” Proc

mposium on Circuits an,

Orlando, 30 May-2 June 1999, pp. 286-289.

[2] S. Bhanja and N. Ranganathan, “Switching Activity Es-

timation of VLSI Circuits Using Bayesian Networks”

IEEE Transactions on VLSI Systems, Vol. 11, No. 4, 2003,

pp. 558-567. doi:10.1109/TVLSI.2003.81614

an Diego,

cuits and Systems, Vol. 15,

[3] M. Xakellis and F. Najm, “Statistical Estimation of the

Switching Activity in Digital Circuits,” Proceedings of

the Conference on Design Automation DAC, S

6-10 June 1994, pp. 728-733.

[4] M. Nemani and F. Najm, “Towards a High-Level Power

Estimation Capability,” IEEE Transactions on Computer-

Aided Design of Integrated Cir

No. 6, 1996, pp. 588-598. doi:10.1109/43.503929

[5] A. Ghosh, S. Devadas, K. Keutzer and J. White, “Esti ma-

tion of Average Switching Activity in Combinational and

Sequential Circuits,” Proceedings of the Conference on

E Transactions on Computer-aided Design of

Design Automation DAC, Anaheim, 8-12 June 1992, pp.

253-259.

[6] C. S. Ding, C. Y. Tsui and M. Pedram, “Gate-Level

Power Estimation Using Tagged Probabilistic Simula-

tion,” IEE

Integrated Circuits and Systems, Vol. 17, No. 11, 1998,

pp. 1099-1107. doi:10.1109/43.736184

[7] S. M. Kang, “Accurate Simulation of Power Dissipation

in VLSI Circuits,” IEEE Transactions on Solid-State Cir-

cuits, Vol. 21, No. 5, 1986, pp. 889-891.

doi:10.1109/JSSC.1986.1052622

[8] R. Burch, F. N. Najm, P. Yang and T. N. Trich, “A Monte

Carlo Approach for Power Estimation,”

tions on VLSI Systems, Vol. 1, No. IEEE Transac-

1, 1993, pp. 63-71.

doi:10.1109/92.219908

[9] J. Monteiro, S. Daved, A. Chos, K. Keutzer and J. White,

“Estimation of Average Switching Activity in Combin

tional Logic Circuits Usa-

ing Symbolic Simulation,” IEEE

Transactions on Computer-aided Design of Integrated

Circuits and Systems, Vol. 16, No. 1, 1997, pp. 121-127.

doi:10.1109/43.559336

[10] M. F. Fouda, M. B. Abdelahlim and H. H. Amer, “Aver-

age and Maximum Power Consumption of Digital CMOS

Circuits Using Logic Pic

tures,” Proceedings of the Inter-

ics

994, pp. 446-455. doi:10.1109/92.335013

national Conference on Computer Engineering and Sys-

tems ICCES, Cairo, 14-16 December 2009, pp. 14-16.

[11] M. F. Fouda, M. B. Abdelahlim and H. H. Amer, “Power

Consumption of Sequential CMOS Circuits Using Logic

Pictures,” Proceedings of the Biennial Baltic Electron

Conference BEC, Tallinn, 4-6 October 2010, pp. 133-136.

[12] M. H. Amin, M. F. Fouda, A. M. Eltantawy, M. B. Abde-

lahlim and H. H. Amer, “Generalization of Logic Pic-

ture-Based Power Estimation Tool,” Proceedings of the

First Annual International Conference on Energy Aware

Computing ICEAC, Cairo, 16-18 December 2010, pp.

133-136.

[13] F. Najm, “A Survey of Power Estimation Techniques in

VLSI Circuits,” IEEE Transactions on VLSI Systems, Vol.

2, No. 4, 1

l. 12,

[14] F. Najm, “Transition Density: A New Measure of Activ-

ity in Digital Circuits,” IEEE Transactions on Computer-

Aided Design of Integrated Circuits and Systems, Vo

No. 2, 1993, pp. 310-323. doi:10.1109/43.205010

Copyright © 2013 SciRes. CS