X. WANG ET AL.

Copyright © 2013 SciRes. MNSMS

4. Conclusions

In summary, doubly stacked nc-Si based MIS memory

structure was fabricated by plasma enhanced chemical

vapor deposition. C-V and C-t measurement was used to

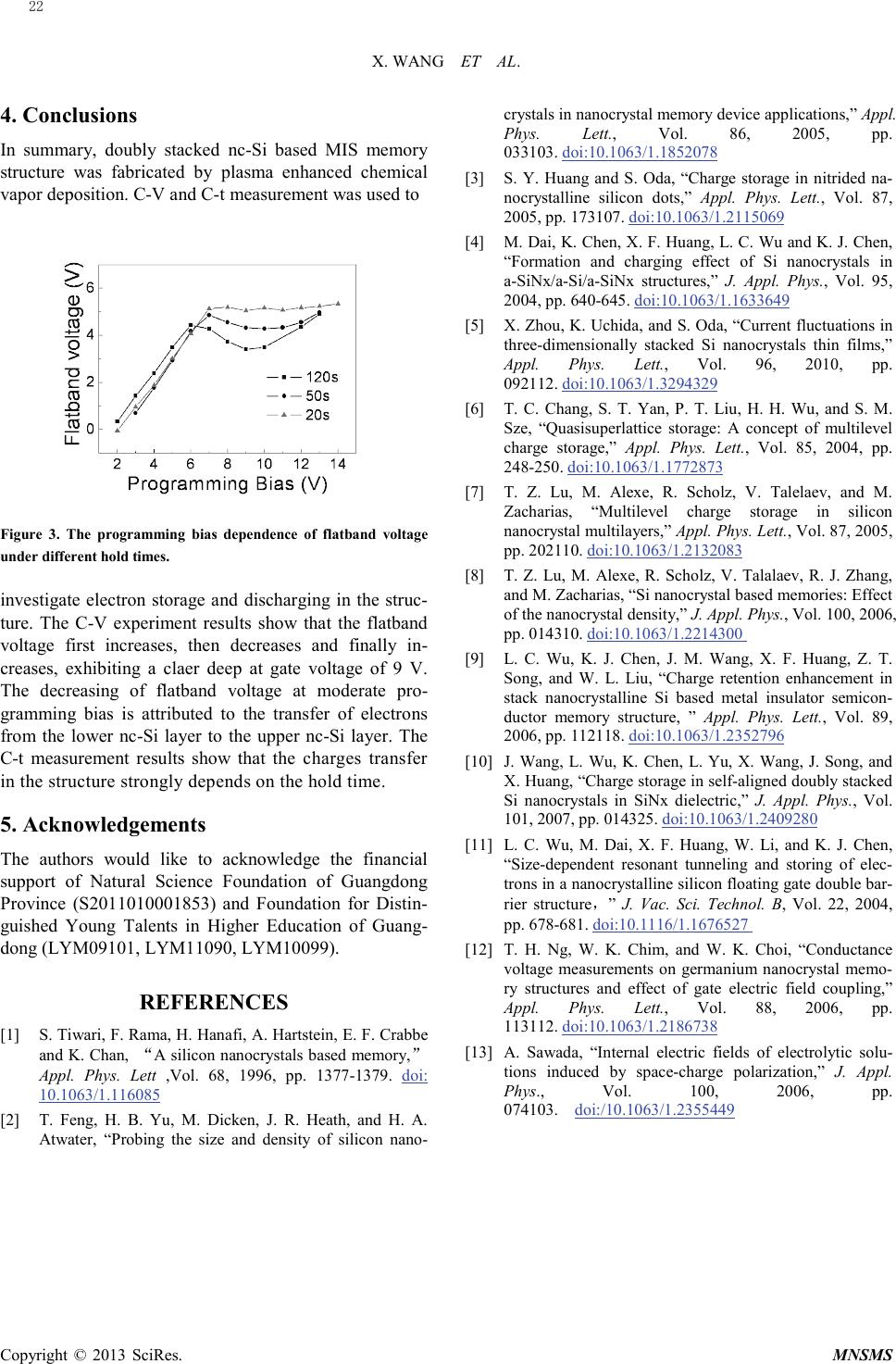

Figure 3. The programming bias dependence of flatband voltage

under different hold times.

investigate electron storage and discharging in the struc-

ture. The C-V experiment results show that the flatband

voltage first increases, then decreases and finally in-

creases, exhibiting a claer deep at gate voltage of 9 V.

The decreasing of flatband voltage at moderate pro-

gramming bias is attributed to the transfer of electrons

from the lower nc-Si layer to the upper nc-Si layer. The

C-t measurement results show that the charges transfer

in the structure strongly depends on the hold time.

5. Acknowledgemen t s

The authors would like to acknowledge the financial

support of Natural Science Foundation of Guangdong

Province (S2011010001853) and Foundation for Distin-

guished Young Talents in Higher Education of Guang-

dong (LYM09101, LYM11090, LYM10099).

REFERENCES

[1] S. Tiwari, F. Rama, H. Hanafi, A. Hartstein, E. F. Crabbe

and K. Chan, “A silicon nanocrystals based memory,”

Appl. Phys. Lett ,Vol. 68, 1996, pp. 1377-1379. doi:

10.1063/1.116085

[2] T. Feng, H. B. Yu, M. Dicken, J. R. Heath, and H. A.

At water , “Probing the size and density of silicon nano-

crystals in nanocrystal memory device applications,” Appl.

Phys. Lett., Vol. 86, 2005, pp.

033103. doi:10.1063/1.1852078

[3] S. Y. Huang and S. Oda, “Charge storage in nitrided na-

nocrystalline silicon dots,” Appl. Phys. Lett., Vol. 87,

2005, pp. 173107. doi:10.1063/1.2115069

[4] M. Dai, K. Chen, X. F. Huang, L. C. Wu and K. J. Chen,

“Formation and charging effect of Si nanocrystals in

a-SiNx/a-Si/a-SiNx stru ctures,” J. Appl. Phys., Vol. 95,

2004, pp. 640-645. doi:10.1063/1.1633649

[5] X. Zhou, K. Uchida, and S. Oda, “Current fluctuations in

three-dimensionally stacked Si nanocrystals thin films,”

Appl. Phys. Lett., Vol. 96, 2010, pp.

092112. doi:10.1063/1.3294329

[6] T. C. Chang, S. T. Yan, P. T. Liu, H. H. Wu, and S. M.

Sze, “Quasisuperlattice storage: A concept of multilevel

charge storage,” Appl. Phys. Lett., Vol. 85, 2004, pp.

248-250. doi:10.1063/1.1772873

[7] T. Z. Lu, M. Alexe, R. Scholz, V. Talelaev, and M.

Zacharias , “Multilevel charge storage in silicon

nanocrystal multilayers,” Appl. Phys. Lett., Vol. 87, 2005,

pp. 202110. doi:10.1063/1.2132083

[8] T. Z. Lu, M. Alexe, R. Scholz, V. Talalaev, R. J. Zhang,

and M. Zacharias, “Si nanocrystal based memories: Effect

of the nanocrystal density,” J. Appl. Phys., Vol. 100, 2006,

pp. 014310. doi:10.1063/1.2214300

[9] L. C. Wu, K. J. Chen, J. M. Wang, X. F. Huang, Z. T.

Song, and W. L. Liu, “Charge retention enhancement in

stack nanocrystalline Si based metal insulator semicon-

ductor memory structure, ” Appl. Phys. Lett., Vol. 89,

2006, pp. 112118. doi:10.1063/1.2352796

[10] J. Wang, L. Wu, K. Chen, L. Yu, X. Wang, J. Song, and

X. Huang, “Charge storage in self-aligned doubly stacked

Si nanocrystals in SiNx dielectric,” J. Appl. Phys., Vol.

101, 2007, pp. 014325. doi:10.1063/1.2409280

[11] L. C. Wu, M. Dai, X. F. Huang, W. Li, and K. J. Chen,

“Size-dependent resonant tunneling and storing of elec-

trons in a nanocrystalline silicon floating gate double bar-

rier structure,” J. Vac. Sci. Technol. B, Vol. 22, 2004,

pp. 678-681. doi:10.1116/1.1676527

[12] T. H. Ng, W. K. Chim, and W. K. Choi, “Conductance

voltage measurements on germanium nanocrystal memo-

ry structures and effect of gate electric field coupling,”

Appl. Phys. Lett., Vol. 88, 2006, pp.

113112. doi:10.1063/1.2186738

[13] A. Sawada, “Internal electric fields of electrolytic solu-

tions induced by space-charge polarization,” J. Appl.

Phys., Vol. 100, 2006, pp.

074103. doi:/10.1063/1.2355449