Paper Menu >>

Journal Menu >>

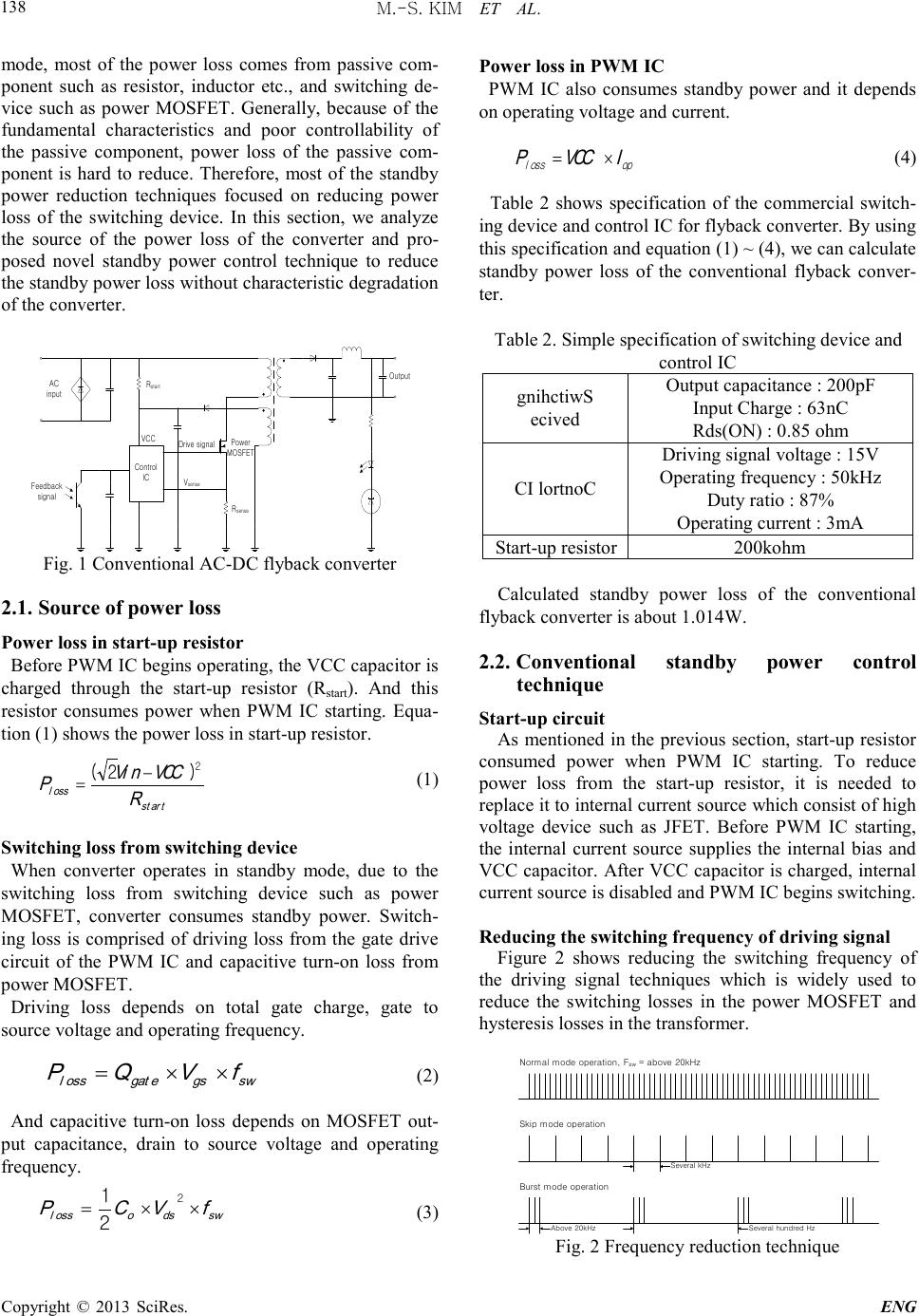

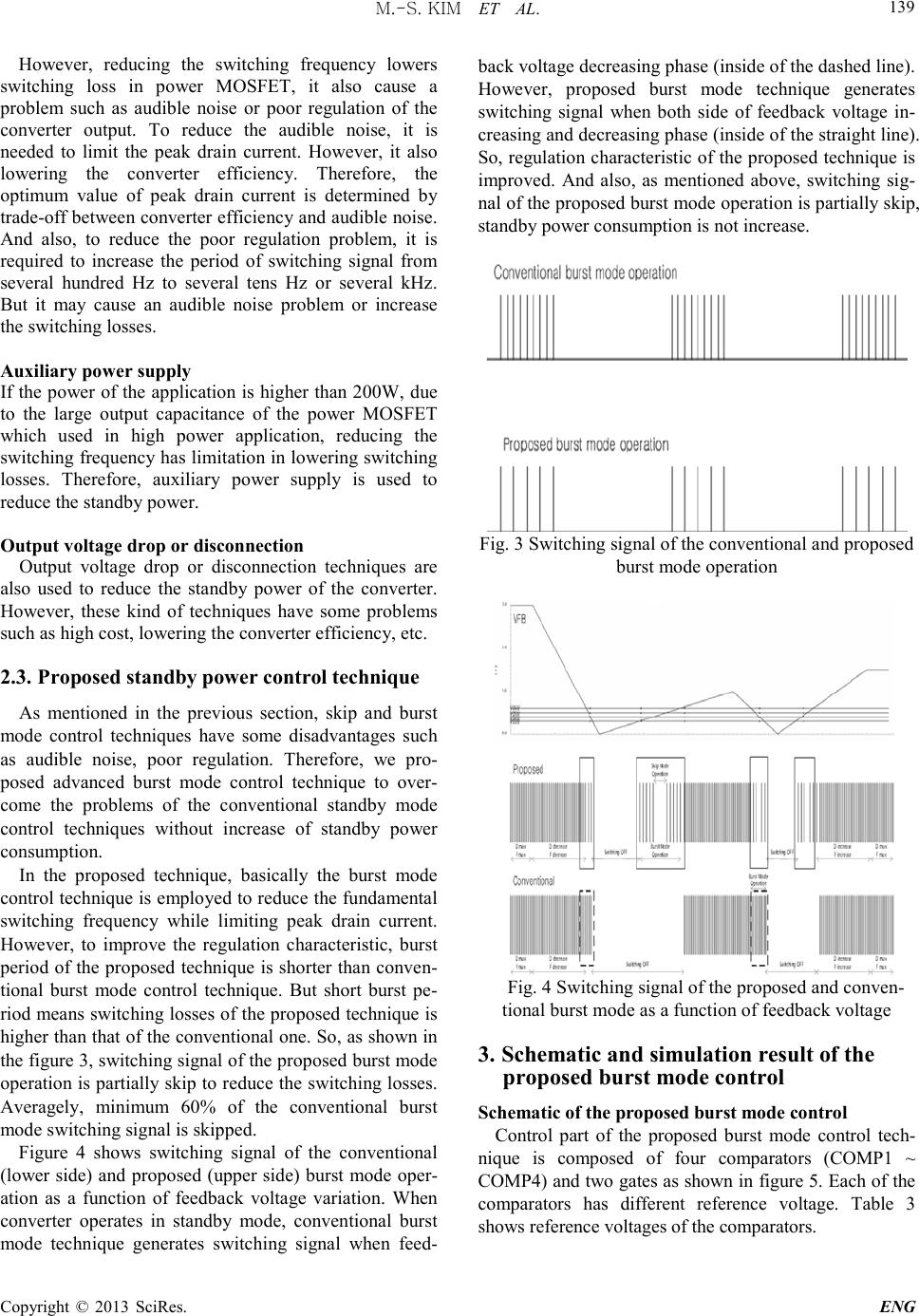

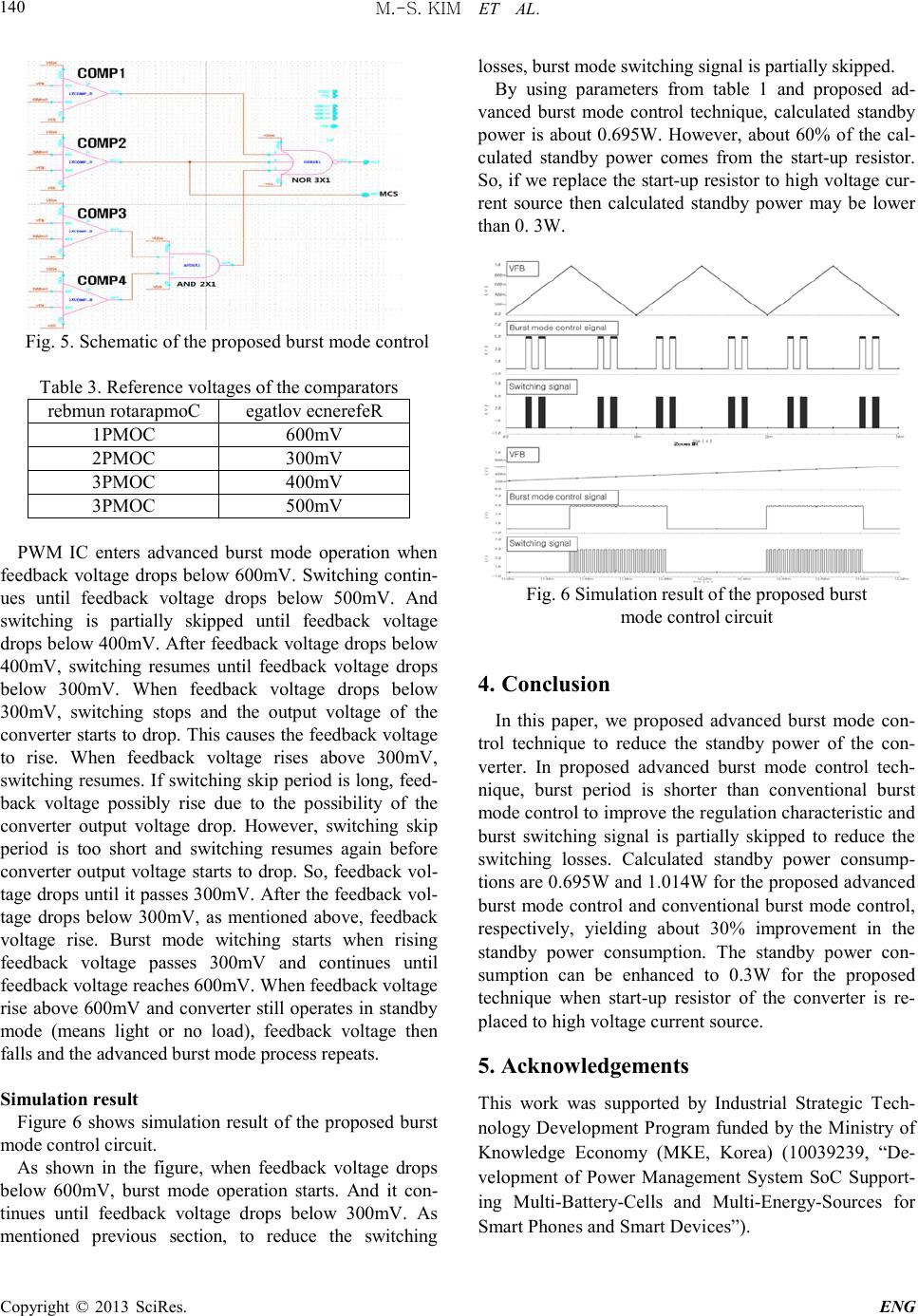

Engineering, 2013, 5, 137-141 doi:10.4236/eng.2013.51b025 Published Online January 2013 (http://www.SciRP.org/journal/eng) Copyright © 2013 SciRes. ENG Advanced Burst Mode Control to Reduce the Standby Power of Flyback Converter Min-Sung Kim1, Hyoung-Woo Kim2, Ji-Hye Jang1, Ki-Hyun Kim2, Kil-Soo Seo2, Nam-Kyun Kim2 and Young-Hee Kim1 1: Department of Electronic En gi neerin g, Changwon National University, Changwon, Rep ubli c of Korea 2: Power Semiconductor Research Center, Korea Electrotechnology Research Inst itute 28-1 Sungju-Dong, S ungsan-Gu, Changwon, 642-120 Republic of Korea Email: youngkim@changwon.ac.kr Received 2013 Abstract This paper we proposed advanced burst mode control technique to reduce the standby power consumption of the switch mode power supply (SMPS). To reduce the standby power consumption, most of the converter use burst mode or skip mode control technique. However Conventional standby mode control techniques have some problems such as audible noise and poor regulation. In proposed techniques, basically, the burst mode control technique is employed to reduce the fund amenta l switc hing fr equenc y while l imiti ng the p eak drai n curre nt. But, in proposed technique, to improve the regulation characteristic, burst period of the proposed technique is shorter than that of the conventional burst mode technique. And also, to reduce the switching loss increase due to the short burst period, burst switching signal of the proposed technique is partially skipped. By using proposed advanced burst mode control technique, calculated standby power is 0.695W while standby power of the conventional burst mode control is 1.014W. Keywords: Standby power, Flyback converter, PWM IC, SMPS 1. Introduction Many electrical and electronics devices operate in low power or standby power mode, in readiness for an exter- nally activated signal. This external signal can be acti- vated by remote control, network connection, etc. Re- cently, the standby mode is widely adopted for many kinds of applications as users require devices that are always available and can be remotely turned on and off. Electronic devices operate in standby mode are always on and consumes some electric energy required to supply the micro-controller a nd other standby circuitry [1]. According to the report from Lawrence Berkley Na- tional Laboratory (LBNL), the standby power in many countries accounts for more than 10% ~ 15% of national residential electr ic ity use [2-3]. Due to the necessity of standby power reduction in electronic devices, many kinds of standby power control techniques such as burst mode control, skip mode control, etc., were invented. However, these kinds of techniques have some disadvantages as shown in table 1 [4]. In thi s pap er, advanced burst mode control technique to reduce the standby power consumption is proposed. In proposed techniques, basically, the burst mode control technique is employed to reduce the fundamental switc hi n g fre quenc y while lim iting the peak d r a in current. But, in proposed technique, to improve the regulation characteristic, burst period is shorter than that of the conventional burst mode technique. And also, to reduce the switching loss increase due to the short burst period of the proposed technique, burst switching signal is par- tially skipped. By using proposed advanced burst mode control technique, calculated standby power is 0.695W while standby power of the conventional burst mode control is 1.014W. Table 1. Conventional standby mode control method doMe egatnavdA egatnavdasiD edom pikS noitaluger dooG elbidua hgiH esion edom tsruB elbidua woL esion noitaluger rooP 2. Power loss of the converter Figure 1 shows conventional circuit of the AC-DC fly- back converter. When converter operates in standby  M.-S. KIM ET AL. Copyright © 2013 SciRes. ENG 138 opl oss IVCCP ×= start l oss R VCCVi n P 2 )2( − = mode, most of the power loss comes from passive com- ponent such as resistor, inductor etc., and switching de- vice such as power MOSFET. Generally, because of the fundamental characteristics and poor controllability of the passive component, power loss of the passive com- ponent is hard to reduce. Therefore, most of the standby power reduction techniques focused on reducing power loss of the switching device. In this section, we analyze the source of the power loss of the converter and pro- posed novel standby power control technique to reduce the standby power loss without characteristic degradation of the converter. AC input Output Power MOSFET Drive signal Rsense Rstart VCC Vsense Control IC Feedback signal Fig. 1 Conventiona l AC-DC flyback converter 2.1. Source of power loss Power loss in start-up resistor Before PWM IC begins operating, the VCC capacitor is charged through the start-up resistor (Rstart). And this resistor consumes power when PWM IC starting. Equa- tion (1) shows the po wer loss in start -up resi s t or. (1) Switc hing loss from switching device When converter operates in standby mode, due to the switching loss from switching device such as power MOSFET, converter consumes standby power. Switch- ing loss is comprised of driving loss from the gate drive circuit of the PWM IC and capacitive turn-on loss from po wer MOSFE T. Driving loss depends on total gate charge, gate to source vo l tage and operating f req uenc y. (2) And capacitive turn-on loss depends on MOSFET out- put capacitance, drain to source voltage and operating frequency. (3) Power loss in PWM IC PWM IC also consumes standby power and it depends on oper ating voltage and curre nt. (4) Table 2 shows specification of the commercial switch- ing de vi ce and control IC for flyback converter. By using this specifica tion a nd equatio n ( 1) ~ (4), we can calcula te standby power loss of the conventional flyback conver- ter. Table 2. Simple specification of switching device and control IC gnihctiwS ecived Output capacitance : 200pF Input Charge : 63n C Rds(ON) : 0.85 ohm CI lortnoC Driving s ignal vol tage : 15V Ope rati ng frequency : 50kHz Duty ratio : 8 7% Ope rati ng cur rent : 3mA Start-up re si st or 200kohm Calculated standby power loss of the conventional flyback converter is about 1.014W. 2.2. Conventional standby power control technique Start-up c ircuit As mentioned in the previous section, start-up resistor consumed power when PWM IC starting. To reduce power loss from the start-up resistor, it is needed to replace it to internal current source which consist of high voltage device such as JFET. Before PWM IC starting, the internal current source supplies the internal bias and VCC capacitor. After VCC capacitor is charged, internal current source is disabled and PWM IC b egins s witchin g. Reducing t he switching frequency of driving signal Figure 2 shows reducing the switching frequency of the driving signal techniques which is widely used to reduce the switching losses in the power MOSFET and hysteresis losse s i n the tran s former. Normal mode operation, F sw = above 20kHz Skip mode operation Burst mode operation Several kHz Above 20kHzSeveral hundred Hz Fig. 2 Freque ncy r educ tion technique swgsgat elossfVQP ××= swdsoloss fVCP ××= 2 2 1  M.-S. KIM ET AL. Copyright © 2013 SciRes. ENG 139 However, reducing the switching frequency lowers switching loss in power MOSFET, it also cause a problem such as audible noise or poor regulation of the converter output. To reduce the audible noise, it is needed to limit the peak drain current. However, it also lowering the converter efficiency. Therefore, the optimum value of peak drain current is determined by trade-off between converter efficiency and audible noise. And also, to reduce the poor regulation problem, it is required to increase the period of switching signal from several hundred Hz to several tens Hz or several kHz. But it may cause an audible noise problem or increase the s witchin g losses. Auxiliar y pow er supply If the power of the application is higher than 200W, due to the large output capacitance of the power MOSFET which used in high power application, reducing the switching freq uency has limitatio n in lowering switchin g losses. Therefore, auxiliary power supply is used to reduce the standby power. Output v oltage drop or disconnectio n Output voltage drop or disconnection techniques are also used to reduce the standby power of the converter. However, these kind of techniques have some problems such as high cost, lo wering the converter efficiency, etc. 2.3. Proposed stan dby power contro l techn iqu e As mentioned in the previous section, skip and burst mode control techniques have some disadvantages such as audible noise, poor regulation. Therefore, we pro- posed advanced burst mode control technique to over- come the problems of the conventional standby mode control techniques without increase of standby power consumption. In the proposed technique, basically the burst mode control technique is employed to reduce the fundamental switching frequency while limiting peak drain current. However, to improve the regulation characteristic, burst period of the proposed technique is shorter than conven- tional burst mode control technique. But short burst pe- riod means s witching losse s of the proposed technique is higher than t hat of t he conve ntio nal one. So, as shown in the fi gure 3, s witchi n g signa l o f the proposed burst mode operatio n is partiall y skip to r educe the switching losses. Averagely, minimum 60% of the conventional burst mode switc hing signal is skipped. Figure 4 shows switching signal of the conventional (lower side) and proposed (upper side) burst mode oper- ation as a function of feedback voltage variation. When converter operates in standby mode, conventional burst mode technique generates switching signal when feed- back voltage decreasing phase (inside of the dashed line). However, proposed burst mode technique generates switching signal when both side of feedback voltage in- creasing and decreasing phase ( inside of t he strai ght line). So, regulation characteristic of the proposed technique is improved. And also, as mentioned above, switching sig- nal of the proposed burst mode operation is partially skip, standby power consumption is not increase. Fig. 3 Switching signal of the conventional and proposed burst mode operation Fig. 4 Switching signal of the pro posed and conve n- tional burst mode as a function of feedback voltage 3. Schematic and simulation result of the proposed burst mode control Schematic of the proposed burst mode control Control part of the proposed burst mode control tech- nique is composed of four comparators (COMP1 ~ COMP4) and two gates as shown in figure 5. Each of the comparators has different reference voltage. Table 3 shows reference voltages of the comparators.  M.-S. KIM ET AL. Copyright © 2013 SciRes. ENG 140 Fig. 5. Schematic of the proposed burst mode control Table 3. Reference voltages of the comparators rebmun rotarapmoC egatlov ecnerefeR PMOC1 600mV PMOC2 300mV PMOC3 400mV PMOC3 500mV PWM IC enters advanced burst mode operation when feedback voltage drops below 600mV. Switching contin- ues until feedback voltage drops below 500mV. And switching is partially skipped until feedback voltage drops below 400mV. After feedback voltage drops below 400mV, switching resumes until feedback voltage drops below 300mV. When feedback voltage drops below 300mV, switching stops and the output voltage of the conver ter starts to drop. This causes the feedback voltage to rise. When feedback voltage rises above 300mV, switching r esumes. If switching ski p period is long, feed- back voltage possibly rise due to the possibility of the converter output voltage drop. However, switching skip period is too short and switching resumes again before converter output voltage starts to drop. So, feedback vol- tage drop s until it passes 300mV. After the feedbac k vol- tage drops below 300mV, as mentioned above, feedback voltage rise. Burst mode witching starts when rising feedback voltage passes 300mV and continues until feedback voltage reaches 600mV. When feedback voltage rise above 600mV and converter still operates in standby mode (means light or no load), feedback voltage then falls and the advanced burst mode proces s repeats. Simulation result Figure 6 shows simulation result of the proposed burst mode control circuit. As shown in the figure, when feedback voltage drops below 600mV, burst mode operation starts. And it con- tinues until feedback voltage drops below 300mV. As mentioned previous section, to reduce the switching losses, burst mode switching signal is partially skipped. By using parameters from table 1 and proposed ad- vanced burst mode control technique, calculated standby power is about 0.695W. However, about 60% of the cal- culated standby power comes from the start-up resistor. So, if we replace the start-up resistor to high voltage cur- rent source then calculated standby power may be lower than 0. 3W. Fig. 6 Simulation result of the prop osed bu rst mode control circuit 4. Conclusion In this paper, we proposed advanced burst mode con- trol technique to reduce the standby power of the con- verter. In proposed advanced burst mode control tech- nique, burst period is shorter than conventional burst mode control to improve the regulation characteristic and burst switching signal is partially skipped to reduce the switching losses. Calculated standby power consump- tions are 0.695W and 1.014W for the proposed advanced burst mode control and conventional burst mode control, respectively, yielding about 30% improvement in the standby power consumption. The standby power con- sumption can be enhanced to 0.3W for the proposed technique when start-up resistor of the converter is re- placed to high voltage c ur re nt so ur ce . 5. Acknowledgements This work was supported by Industrial Strategic Tech- nology Development Program funded by the Ministry of Knowledge Economy (MKE, Korea) (10039239, “De- velopment of Power Management System SoC Support- ing Multi-B a tte ry-Cells and Multi-Energy-Sources for Smart Phones and Smart Devices”).  M.-S. KIM ET AL. Copyright © 2013 SciRes. ENG 141 REFERENCES [1] L. McGarry, “The standby power challenge” Proc. Of IEEE AGEC, pp. 56-62, 2004 [2] Alan Meier, Wolfgang Huber and Karen Rosen, “Reduc- ing Leaking Electricity to 1 Watt”, The 1998 ACEEE Summer Study on Energy in Buildings, August 1998. [3] J. P . Ross and Alan M eier, “Whol e-Hou se Measurements of Standby Power Consumption”, International Confe- rence on Energy Efficiency in Appliances, September, 2000. [4] Hang-Seok Choi and D. Y. Huh, “Techniques to minim- ize Power Consumption of SMPS in Standby Mode”, Po wer E lectron ics Sp ecialist s Conferen ce200 5, P ESC, pp. 2817-2822, IEEE 36th, 2005. [5] Yoh Matsushita, “Design for low electric power during standby state of fax-copier machine”, International Sym- posium On Environmentally Conscious Design and In- verse Manufactur ing, pp. 391-395. 1999. [6] A. I. Maswood, Z. K. Yoong, “Digital burst technique in the stand -by operation of a TV power supply”, IEEE IAS Annual Meeting, Industry Applications Conference, pp. 1661-1668, 1999. |