Intelligent Control and Automation

Vol.06 No.02(2015), Article ID:55523,9 pages

10.4236/ica.2015.62012

Adaptation of the Two Sources of Code and One-Hot Encoding Method for Designing a Model of Microprogram Control Unit with Output Identification

Łukasz Smoli?ski*, Alexander Barkalov, Larysa Titarenko

Institute of Computer Engineering and Electronics, University of Zielona Góra, Zielona Góra, Poland

Email: *L.Smolinski@weit.uz.zgora.pl

Copyright © 2015 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received 4 March 2015; accepted 9 April 2015; published 10 April 2015

ABSTRACT

This article presents a proposal for a model of a microprogram control unit (CMCU) with output identification adapted for implementation in complex programmable logic devices (CPLD) equipped with integrated memory modules [1] . An approach which applies two sources of code and one-hot encoding has been used in a base CMCU model with output identification [2] [3] . The article depicts a complete example of processing for the proposed CMCU model. Furthermore, it also discusses the advantages and disadvantages of the approach in question and presents the results of the experiments conducted on a real CPLD system.

Keywords:

CPLD, PAL, UFM, CLB, Two Sources of Code, One-Hot Encoding, CMCU

1. Introduction

Nowadays, complex programmable electronic systems are applied for implementing logic circuits of control units [4] - [9] . However, the issue of reducing the size of a control unit is still a subject of current interest [10] [11] . Reducing the size of used resources makes it possible to improve such indicators as: the speed of performance, power consumption and the size of the realised unit [12] [13] . One of the methods for reducing the size of the control unit is the realization of the control algorithm with the use of the CMCU (compositional microprogram control unit) project methodology [14] . The application of CMCU makes it possible to implement a much smaller number of logical functions realising the task of the control system. The existing project methods based on the CMCU are not dedicated to the solutions realized with the use of programmable devices (CPLD). CPLDs include macrocells of programmable array logic (PAL) with a limited number of terms. To reduce the amount of hardware in the logic circuit of a control unit, the peculiarities of the CPLD and the features of a control algorithm to be implemented should be taken into account. Some of the CPLD family devices are equipped with integrated memory. For example, Altera CPLD devices are equipped with user flesh memory (UFM) [15] , whereas Cypress CPLD devices are equipped with cluster memory blocks (CMB) [16] . This article presents a mathematical model and a design algorithm with two sources of code and one hot encoding which has been adopted to CMCU model with output identification [1] .

2. Background of the CMCU with Output Identification

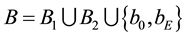

It is assumed that the graph-scheme of the algorithm (GSA) is represented by sets of vertices  where

where

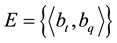

and a set of arcs E where

and a set of arcs E where . It is further assumed that

. It is further assumed that  and

and

is an initial vertex,  is a final vertex,

is a final vertex,  is a set of operator vertices,

is a set of operator vertices,  is a set of conditional vertices. A

is a set of conditional vertices. A

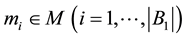

vertex contains a microinstruction  and

and  is a set of data-path microoperations

is a set of data-path microoperations [17] . Each vertex

[17] . Each vertex  contains a single element

contains a single element  of a set of logical conditions

of a set of logical conditions

. A set C of operational linear chains (OLC) for the GSA shall be formed, where each OLC is a sequence of operator vertices and each pair of its adjacent components corresponds to an arc of the GSA.

. A set C of operational linear chains (OLC) for the GSA shall be formed, where each OLC is a sequence of operator vertices and each pair of its adjacent components corresponds to an arc of the GSA.

(1)

(1)

Each OLC  has only one output

has only one output

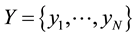

and the bits are represented by variables from the set T:

The project methodology of the microprogram control unit with output identification offers specific positioning of microinstructions in the memory, so as to make it possible to determine the state of the unit, using possibly the smallest number of address signals. The algorithm of positioning microinstruction in the memory consists of the following steps:

1. First, all microinstruction addresses are coded with the use of natural encoding.

2. The value of

3. An address table is created. The table consists of

4. If the outputs

5. If all the output vertices are uniformly represented by

6. If the address of any vertices reaches beyond the range of the current addressing, then:

7. The end.

The codes for each microinstruction are formed as a concatenation of the table’s columns and lines. In such a case, the outputs of the OLC chain are uniformly encoded using variables from the set

The algorithm for designing a model of the CMCU with output identification consists of the following steps:

1. Formation of the set of OLCs.

2. Addressing microinstructions (with shifting operation) and encoding OLC elements.

3. Formation of the control memory content.

4. Formation of the transition table of the CMCU.

5. Formation of the excitation function for the counter.

6. Synthesis of the logic circuit of CMCU.

Figure 1 shows a logical scheme of the CMCU with output identification. The pulse

3. Main Idea behind the Proposed Method

It shall be pointed out that the logic for the CC and CT is implemented as parts of the CPLD. An external PROM chip or memory integrated with the CPLD may be applied to implement the CM. The memory has t outputs, where

The

The

If conditions

take place, the method can be used. As for encoding additional information used by excitation functions for the CT, one-hot encoding will be applied. In such a case, the amount of information that can be stored in free CM is:

Next, an occurrence table is created, with columns

It shall be noted that the collection

Figure 1. Structural diagram of the CMCU with output identification U1.

For the CMCU model with output identification and two sources of code, the memory CM is a source of variables

It shall be highlighted that the maximum length of the logical expressions used for making excitation functions which use the information from the source

For the proposed model with one hot encoding, the maximum length of the logical expressions built on the basis of the information from the collection

The maximum length of logical expressions for the model with one hot encoding, built on the basis of the information from the collection

As a result, the value of the CM and the transition table have been modified on the basis of the occurrence table.

The modified algorithm for designing a model of the CMCU with output identification consists of the following steps:

1. Formation of the set of OLCs.

2. Addressing microinstructions (with shifting operation) and encoding OLC elements.

3. Formation of the control memory content.

4. Formation of the transition table of the CMCU.

5. Formation of the occurrence table.

6. Modification of the control memory content.

7. Modification of the transition table of the CMCU.

8. Formation of the excitation function for the counter and minimization.

9. Synthesis of the logic circuit of CMCU.

Figure 2 presents a modified structure of the CMCU with output identification and the applied method of two sources of code.

4. An Example of the Proposed Method

Figure 3 and Figure 4 present an exemplary algorithm used for the realization by the control unit. This algorithm employs the following variables:

Figure 2. Modified structural diagram of the CMCU with output identification U2.

Figure 3. An example of the algorithm used for the realisation of T1.

Table 1. Initial table of addressing.

Figure 4. Operation chains for the algorithm T1.

Next, the shift operation takes place, resulting in a new address Table 2. Thanks to the shift operation, all the elements

Let us assume that we have a memory module in which

the calculations may be put forward as:

an occurrence Table 6 is created. For the purpose of this example, high values in address bits (there are 7 of them) corresponding to the element

vided into collections

Table 2. Table of addressing after shift operation.

Table 3. OLC elements encoding.

Table 4. Microinstruction encoding.

Table 5. Transition table.

Table 6. Occurrence table.

5. Results and Conclusions

Figure 5 presents the results of the implementation of the model in real hardware. The Alter, a family MAX II device EPM1270 F256C5 equipped with UFM, has been used for tests. Figure 5 depicts the relationship between the obtained reduction in the size of the system (in percentage) and the participation of the source of data

Figure 5. Reduction in the size of the system due to the participation of the source.

1. Formation of the set of OLCs.

2. Addressing microinstructions (with shifting operation) and encoding OLC elements.

3. Formation of the control memory content.

4. Formation of the transition table of the CMCU.

5. Construction of excitation functions for the CT and RG.

6. Minimization of excitation functions.

7. Finding logical expressions―OLC elements which have not undergone minimization―in the minimized excitation functions.

8. Formation of the occurrence table containing most frequently occurring OLC elements which have not undergone minimization.

9. Modification of the control memory content.

10. Modification of the transition table and CM of the CMCU.

11. Formation of the excitation function for the counter and minimization.

12. Synthesis of the logic circuit of CMCU.

Taking the OLC elements, which do not undergo minimization to the collection

Information

Mr. Łukasz Smoli?ski is a scholar within Sub-measure 8.2.2 Regional Innovation Strategies, Measure 8.2 Transfer of knowledge, Priority VIII Regional human resources for the economy Human Capital Operational Programme co-financed by European Social Fund and state budget.

References

- Wiśniewski, R. (2009) Synthesis of Compositional Microprogram Control Units for Programmable Devices. University of Zielona Gora Press, Poland.

- Barkalov, A., Titarenko, L. and Smoli?ski, L. (2014) CMCU Model with Base Structure Dedicated for CPLD Systems. Przegląd Elektroniczny, 12, 25-29.

- Barkalov, A., Titarenko, L. and Smoli?ski, L. (2012) Optimization of Control Unit Based on Construction of CPLD, Pomiary, Automatyka, Kontrola, 58, 93-96.

- Monmasson, E., Idkhajine, L., Cirstea, M., Bahri, I., Tisan, A. and Naouar, M. (2011) FPGAs in Industrial Control Applications. IEEE Transactions on Industrial Informatics, 7, 224-242. http://dx.doi.org/10.1109/TII.2011.2123908

- Kania, D. (2004) The Logic Synthesis for the PAL-Based Complex Programmable Logic Devices. Zeszyty Naukowe, Elektronika, 14, 5-212.

- Kubica D. and Kania D. (2011) Synteza logiczna zespołu funkcji ukierunkowana na minimalizację liczby wykorzystywanych bloków logicznych PAL w oparciu o zmodyfikowany graf wyjść. Pomiary, Automatyka, Kontrola, 57, 737- 740.

- Monmasson, E. and Cirstea, M. (2007) FPGA Design Methodology for Industrial Control Systems―A Review. IEEE Transactions on Industrial Informatics, 54, 1824-1842. http://dx.doi.org/10.1109/TIE.2007.898281

- Garcia-Vargas, I., Senhadji-Navarro, R., Jimenez-Moreno, G., Civit-Balcells, A. and Guerra-Gutierrez, P. (2007) ROM- Based Finite State Machine Implementation in Low Cost FPGAs. IEEE International Symposium on Industrial Electronics, Vigo, 4-7 June 2007, 2342-2347. http://dx.doi.org/10.1109/ISIE.2007.4374972

- Rafla, N. and Davis, B. (2006) A Study of Finite State Machine Coding Styles for Implementation in FPGA. 49th IEEE International Midwest Symposium on Circuits and Systems, Puerto Rico, 6-9 August 2006, 337-341.

- Czerwi?ski, R. and Kania, D. (2009) Synthesis of Finite State Machines for CPLDs. International Journal of Applied Mathematics and Computer Science, 19, 647-659. http://dx.doi.org/10.2478/v10006-009-0052-0

- Anand, B.P. and Saravanan, C.G. (2012) Development of Research Engine Control Unit Using FPGA-Based Embedded Control System. Journal of KONES Powertrain and Transport, 19, 9-18.

- Salauyou, V. and Grzes, T. (2007) FSM State Assignment Methods for Low-Power Design. 6th International Conference on Computer Information Systems and Industrial Management Applications, 2007, CISIM ’07, Minneapolis, 28- 30 June 2007, 345-350.

- Czerwinski, R. and Kania, D. (2012) Area and Speed Oriented Synthesis of FSMs for PAL-Based CPLDs. Microprocessors and Microsystems, 36, 45-61. http://dx.doi.org/10.1016/j.micpro.2011.06.004

- Barkalov, A. and Titarenko, L. (2008) Logic Synthesis for Compositional Microprogram Control Units. Springer, Berlin.

- Altera (2007) Using the UFM in MAX II Devices. www.altera.com/literature/an/an489.pdf

- Cypress (2003) Delta39K ISR CPLD Family. http://pdf.datasheetcatalog.com/datasheet2/9/0pfaeyx4ushkk0zzjksaycgxhqky.pdf

- Baranov, S. (2008) Logic and System Design of Digital Systems. TUT Press, Tallin.

- Maxfield, C. (2004) The Design Warrior’s Guide to FPGAs: Devices, Tools and Flows. Elsevier, Amsterdam.

- Barkalov, A., Titarenko, L. and Smoli?ski, L. (2013) Hardware Reduction for Compositional Microprogram Control Unit Dedicated for CPLD Systems. Proceedings of IEEE East-West Design and Test Symposium-EWDTS 2013, Rostov-on-Don, 27-30 September 2013, 1-6. http://dx.doi.org/10.1109/EWDTS.2013.6673200

- Barkalov, A., Titarenko, L. and Smoli?ski, L. (2014) The Application and Adaptation of the Two Sources of Code and Natural Encoding Method for Designing a Model of Microprogram Control unit with Base Structure. Circuits and Systems, 5, 301-308. http://dx.doi.org/10.4236/cs.2014.512031

- Barkalov, A., Titarenko, L. and Smoli?ski, L. (2011) Optimization of Microprogram Control Unit with Code Sharing. Proceedings of IEEE East-West Design & Test Symposium-EWDTS 2011, Sevastopol, 9-12 September 2011, 55-59. http://dx.doi.org/10.1109/EWDTS.2011.6116573

NOTES

*Corresponding author.