Circuits and Systems

Vol.05 No.12(2014), Article ID:51321,7 pages

10.4236/cs.2014.512031

The Application and Adaptation of the Two Sources of Code and Natural Encoding Method for Designing a Model of Microprogram Control Unit with Base Structure

Łukasz Smoliński*, Alexander Barkalov, Larysa Titarenko

Institute of Computer Engineering and Electronics, University of Zielona Góra, Zielona Góra, Poland

Email: *L.Smolinski@weit.uz.zgora.pl

Copyright © 2014 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received 27 September 2014; revised 28 October 2014; accepted 6 November 2014

ABSTRACT

The article presents a modification to the method which applies two sources of data. The modification is depicted on the example of a compositional microprogram control unit (CMCU) model with base structure implemented in the complex programmable logic devices (CPLD). First, the conditions needed to apply the method are presented, followed by the results of its implementation in real hardware.

Keywords:

CPLD, PAL, UFM, CLB, Two Sources of Code, One-Hot Encoding, Natural Encoding, CMCU

1. Introduction

Control units are very important parts of digital systems [1] -[6] . Nowadays, complex programmable logic devices (CPLD) are widely used for implementing logic circuits of control units [7] [8] . However, the issue of reducing the size of a control unit is still a subject of current interest. Finding a solution to this issue will make it possible to improve such indicators as the speed of performance and the power consumption of the designed system [9] [10] . CPLDs include macrocells of programmable array logic (PAL) with a limited number of terms. To reduce the amount of hardware in the logic circuit of a control unit, the peculiarities of the CPLD and the features of a control algorithm to be implemented should be taken into account. If a control algorithm is represented by a linear graph-scheme of the algorithm (GSA), then a model of the compositional microprogram control unit (CMCU) can be used for its interpretation [11] . It is assumed by the authors that the control memory (CM) of the CMCU can be implemented as external PROM/ROM memory. Some of the CPLD family devices are equipped with integrated memory. For example, Altera CPLD devices are equipped with user flesh memory (UFM) [12] , whereas Cypress CPLD devices are equipped with cluster memory blocks (CMB) [13] . This article presents a mathematical model and a design algorithm with two sources of code and natural encoding which has been modified and adopted to CMCU model with base structure [14] [15] .

2. Background of the CMCU with Base Structure and Two Sources of Code

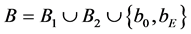

It is assumed that the GSA is represented by sets of vertices  where

where  and a set of arcs

and a set of arcs  where

where . It is further assumed that

. It is further assumed that  and

and  is an initial vertex,

is an initial vertex,  is a final vertex,

is a final vertex,  is a set of operator vertices,

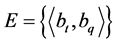

is a set of operator vertices,  is a set of conditional vertices. A vertex contains a microinstruction

is a set of conditional vertices. A vertex contains a microinstruction  and

and  is a set of data-path microoperations

is a set of data-path microoperations  [16] - [18] . Each vertex

[16] - [18] . Each vertex  contains a single element

contains a single element  of a set of logical conditions

of a set of logical conditions . A set

. A set of operational linear chains (OLC) for the GSA shall be formed, where each OLC is a sequence of operator vertices and each pair of its adjacent components corresponds to an arc of the GSA.

of operational linear chains (OLC) for the GSA shall be formed, where each OLC is a sequence of operator vertices and each pair of its adjacent components corresponds to an arc of the GSA.

Each OLC

and the bits are represented by variables from the set

Assuming that the

In Equation (4)

The flip-flops outputs are represented by variables from the set

The second source of information about the state of the system is the unused space of the control memory (CM) [19] [20] . An external PROM chip or memory integrated with the CPLD may be applied to implement the CM. The memory has

Thus, the number of available unused flip-flops is:

The

If the condition

takes place, the method can be used. The number of repetitions of each state occurring as the initial state is counted in the transitions of the algorithm. The states of the system are identified through the outputs

takes place. The collection

The combinational circuit (CC) generates data

The synthesis of the CMCU algorithm includes the following steps:

1) Forming the set of OLCs.

2) Forming the control memory content.

3) Forming the transition table of the CMCU.

4) Counting the occurrence of

5) Dividing the collection

6) Updating the control memory content.

7) Forming the excitation functions for the CT and RG with using two sources of code.

8) Synthesis of the logic circuit of CMCU.

Figure 1 presents a structural diagram of the CMCU with two sources of code. The pulse Start causes loading of the first microinstruction address into a counter CT and set up of a fetch flip-flop TF. If

3. Main Idea behind the Proposed Method

The excitation functions generating data for the counter CT and register RG in Equation (12) and Equation (13)

Figure 1. Structural diagram of CMCU U1.

are built with the use of logical terms. Let

Functions from the collections

The maximum length of a term built with the use of information from the collection

The second factor which has a direct influence on the size of the designed system is the possibility of minimizing the excitation functions for the counter CT and register RG. As far as the method with two sources of code is concerned, this possibility is degraded under negative conditions, compared to the method with one source of code. For example, having the OLC elements encoded as in Table 1 and the function for the method with one source of code designed in the following way:

The excitation function

For the analyzed example, the excitation function

In Equation (18), 1 is subtracted to take into account the case when microinstruction is not the source of code. This will be marked by code zero. This code will be not used in excitation functions. To encoding

Table 1. OLC items with base structure.

Table 2. OLC items with two sources of code and one-hot encoding.

elements is used natural encoding. In order to reduce the maximum length of the terms built on the basis of the collection

In such a case, the maximum length of a term built with the use of information from the collection

In the analyzed example for the method with two sources of code and natural encoding, as in Table 3, the function

The excitation function

Table 3. OLC items two sources of code and natural encoding.

Figure 2. Reduction in the size of the system due to the participation of the source.

Figure 3. Reduction in the size of the system by free bits of memory.

basis of data from this collection. Furthermore, using natural encoding enables transferring a greater amount of information to the collection (source)

4. Results and Conclusions

Figure 2 and Figure 3 present the results of the implementation of the model in real hardware. The Altera family MAX II device EPM1270 F256C5 equipped with UFM has been used for tests. The results presented in Figure 2 and Figure 3 have been obtained from research conducted on 200 randomly generated CMCU models with the following properties:

Figure 3 presents the relationship between the obtained reduction in the size of the system (in percentage) and the value of free bits used to representation information from the source

References

- Łuba, T. (2004) Synteza Układów Logicznych. Warsaw University of Technology Press, Warsaw.

- Baranov, S. (1994) Logic Synthesis for Control Automata. Kluwer Academic Publishers, Israel. http://dx.doi.org/10.1007/978-1-4615-2692-6

- DeMicheli, G. (1994) Synthesis and Optimization of Digital Circuits. McGraw-Hill, Boston.

- Milik, A. and Hrynkiewicz, E. (2012) Synthesis and Implementation of Reconfigurable PLC on FPGA Platform. International Journal of Electronics and Telecommunications, 58, 85-94. http://dx.doi.org/10.2478/v10177-012-0012-8

- Barkalov, A. and Węgrzyn, M. (2006) Design of Control Units with Programmable Logic. University of Zielona Góra Press, Zielona Góra.

- Klimowicz, A. and Salauyou, V. (2012) The Synthesis of Combined Mealy and Moore Machines Structural Model Using Values of Output Variables as Codes of States. 15th Euromicro Conference on Digital System Design (DCD), Izmir, 5-8 September 2012, 789-794. http://dx.doi.org/10.1109/DSD.2012.130

- Kubica, M. and Kania, D. (2011) Synteza Logiczna Zespołu Funkcji Ukierunkowana na Minimalizacje Liczby Wykorzystywanych Bloków Logicznych PAL w Oparciu o Zmodyfikowany Graf Wyjść. Pomiary, Automatyka, Kontrola, 57, 737-740.

- Altera (2009) Max II Device Handbook. http://www.altera.com/literature/hb/max2/max2_mii5v1.pdf

- Czerwinski, R. and Kania, D. (2012) Area and Speed Oriented Synthesis of FSMs for PAL-based CPLDs. Microprocessors & Microsystems, 36, 56-61. http://dx.doi.org/10.1016/j.micpro.2011.06.004

- Salauyou, V. and Grzes, T. (2007) FSM State Assignment Methods for Low-Power Design. 6th International Conference on Computer Information Systems and Industrial Management Applications, Minneapolis, 28-30 June 2007, 345-350. http://dx.doi.org/10.1109/CISIM.2007.32

- Barkalov, A. and Titarenko, L. (2008) Logic Synthesis for Compositional Microprogram Control Units. Springer. http://dx.doi.org/10.1007/978-3-540-69285-0

- Altera (2007) Using the UFM in MAX II Devices. www.altera.com/literature/an/an489.pdf

- Cypress (2003) Delta39K ISR CPLD Family. http://pdf.datasheetcatalog.com/datasheet2/9/0pfaeyx4ushkk0zzjksaycgxhqky.pdf

- Barkalov, A., Titarenko, L. and Smoliński, L. (2013) Hardware Reduction for Compositional Microprogram Control Unit Dedicated for CPLD Systems. Proceedings of IEEE East-West Design and Test Symposium EWDTS’13, Rostov- on-Don, 27-30 September 2013, 1-6. http://dx.doi.org/10.1109/EWDTS.2013.6673200

- Barkalov, A., Titarenko, L. and Smoliński, L. (2014) CMCU Model with Base Structure Dedicated for CPLD Systems. Przegląd Elektroniczny. (in Press)

- Baranov, S. (2008) Logic and System Design of Digital Systems. TUT Press, TelAviv.

- Adamski, M. and Barkalov, A. (2006) Architectural and Sequential Synthesis of Digital Devices. University of Zielona Góra Press, Zielona Góra.

- Wisniewska, M., Wisniewski, R. and Adamski, M. (2009) Reduction of the Microinstruction Length in the Designing Process of Microprogrammed Controllers. Przeglad Elektroniczny, 11, 114-117.

- Barkalov, A., Titarenko, L. and Smoliński, L. (2012) Optimization of Control Unit based on Construction of CPLD. Pomiary, Automatyka, Kontrola, 58, 93-96.

- Barkalov, A., Titarenko, L. and Smoliński, L. (2011) Optimization of Microprogram Control Unit with Code Sharing. Proceedings of IEEE East-West Design and Test Symposium (EWDTS), Sevastopol, 9-12 September 2011, 55-59. http://dx.doi.org/10.1109/EWDTS.2011.6116573

- Maxfield, C. (2004) The Design Warrior’s Guide to FPGAs: Devices, Tools and Flows. Elseveir.

- Wiśniewski, R. (2009) Synthesis of Compositional Microprogram Control Units for Programmable Devices. University of Zielona Góra Press, Zielona Góra.

- Barkalov, A. and Titarenko, L. (2009) Logic Synthesis for FSM-Based Control Units. Springer, Zielona Góra. http://dx.doi.org/10.1007/978-3-642-04309-3

- Kołopieńczyk, M. (2008) Application of Address Converter for Decreasing Memory Size of Compositional Microprogram Control Unit with Code Sharing. Lecture Notes in Control and Computer Science, 12, 88-96.

- Bieganowski, J. (2011) Synthesis of Microprogram Control Units Oriented toward Decreasing the Number of Macrocells of Addressing Circuit. Lecture Notes in Control and Computer Science, 17, 103-109.

- Salauyou, V. and Klimowicz, A. (2010) Synteza logiczna układów cyfrowych w strukturach programowalnych. Oficyna Wydawnicza Politechniki Białostockiej, Białystok.

Information

Mr. Łukasz Smoliński is a scholar within Sub-measure 8.2.2 Regional Innovation Strategies, Measure 8.2 Transfer of knowledge, Priority VIII Regional human resources for the economy Human Capital Operational Programme co-financed by European Social Fund and state budget.

NOTES

*Corresponding author.