Circuits and Systems

Vol.07 No.13(2016), Article ID:72393,32 pages

10.4236/cs.2016.713349

Comparative Methodical Assessment of Established MOSFET Threshold Voltage Extraction Methods at 10-nm Technology Node

Yashu Swami, Sanjeev Rai

ECED, MNNIT Allahabad, Allahabad, India

Copyright © 2016 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Received: May 1, 2016; Accepted: May 18, 2016; Published: November 30, 2016

ABSTRACT

Threshold voltage (VTH) is the most evocative aspect of MOSFET operation. It is the crucial device constraint to model on-off transition characteristics. Precise VTH value of the device is extracted and evaluated by several estimation techniques. However, these assessed values of VTH diverge from the exact values due to various short channel effects (SCEs) and non-idealities present in the device. Numerous prevalent VTH extraction methods are discussed. All the results are verified by extensive 2-D TCAD simulation and confirmed through analytical results at 10-nm technology node. Aim of this research paper is to explore and present a comparative study of largely applied threshold extraction methods for bulk driven nano-MOSFETs especially at 10-nm technology node along with various sub 45-nm technology nodes. Application of the threshold extraction methods to implement noise analysis is briefly presented to infer the most appropriate extraction method at nanometer technology nodes.

Keywords:

Threshold Voltage, Constant Current Source Technique, Linear Extrapolation Technique, Threshold Voltage Estimation Techniques, Short Channel Effects, Drift Diffusion Model, Resistive Load Inverter, Noise Margin Analysis

1. Introduction

Incessant abridging of IC technology, together with precision of VTH control techniques and reduction in SCE, is asserting the VTH to very low values. For proper operation of MOSFET, we need to evaluate exact threshold voltage (VTH). Perfectly appraised VTH is required to provide proper gate control over device channel conduction (see Figure 1). The tens of millivolts miscalculation cannot be neglected as it can prompt serious errors in circuit functionality. Especially for robust nano-scale design of analog circuits with high speed operation, precise valuation of VTH is essential to illustrate the exact device behaviour [1] [2] [3] [4] . Device matching also depends on the estimated VTH values. VTH is frequently used for accessing and predicting device performance. It is also commonly used to check the inconsistency due to manufacturing process technological parameter fluctuations. Other applications of VTH can be listed as to evaluate reliability factors such as radiation damage, hot carrier, stress, temperature instability, ageing degradation etc.

The threshold voltage parameter is largely extracted directly from the transfer characteristics of the device. There is no critical point in the ID-VGS curve that can be recognized as threshold point due to sub-threshold leakage current. This creates vagueness in VTH estimation. The weak inversion region shows exponential deviations while strong inversion shows linear/quadratic deviations. However, the VTH is identified amid weak and strong inversion transition region [5] [6] . VTH also depends on several device parameters (Gate width, Gate Overlap, Gate length, biased bulk, temperature etc.) and process technology limitations (Cox, tox, doping concentration (NA) etc.) [7] [8] . This makes VTH estimation more challenging.

In consideration to the above, this paper presents the study and analysis of numerous VTH extraction methods at various sub 45-nm technology node. The outcomes of the analysis are implemented on a simple resistive load inverter for computing noise margins to infer the performance of various threshold voltage extraction methods at sub 45-nm technology node.

Rest of the paper is organized as follows. Section 2 categorizes several threshold voltage extraction methods on the basis of their assessment methodology. Section 3 to Section 8 discuss and evaluate the various mentioned threshold voltage extraction methods at 10-nm technology node and other sub 45-nm technology nodes. Further, Section 9 presents the tabulated compiled simulation results, comparison and discussion for various sub 45-nm technology nodes. Application of the threshold extraction methods to implement noise analysis is briefly presented in Section 10. Finally, concluding remarks

Figure 1. Source referred n-channel MOS transistor biasing.

are conferred in Section 11.

2. Threshold Voltage Estimation Techniques

Ideally, VTH of a device is the critical gate voltage below which the drain to source current (ID) is zero, But practically, sub-threshold leakage current exists for VGS below VTH. As the drain current doesn’t drop abruptly to zero and hence, it becomes challenging to precisely determine the critical point at which switching of ID takes place. Due to this reason, several procedures presented in literature use diverse descriptions to extract the VTH of the MOSFET but still has a scope for improvement to correctly evaluate VTH [9] [10] . This paper revisits VTH extraction techniques and examines these for simplified square-sized NMOS device at 10-nm technology node. For precise evaluation of the methods, the process is reiterated in similar conditions on other sub 45-nm technology nodes [11] [12] .

For simplicity, the threshold extraction methods have been categorized into six main groups on the basis of their assessment methodology as:

1) ID based extraction methods;

2) Derivative of ID based extraction methods;

3) Integral of ID based extraction methods;

4) Self-extraction methods;

5) Deviation based extraction methods;

6) Hybrid extraction methods.

It is considered that the threshold voltage changes with the change in the operating region of the MOSFET specifically in linear/ triode region and saturation region. Distinctive efforts are made to accurately calculate the VTH in both the operating regions [13] [14] [15] . Hence the corresponding respective values of VTH are evaluated as VLIN and VTSAT for all the discoursed methods on our test device. Figure 1 shows the basic biasing settings for n-channel MOSFET. The test device considered is a square-sized uniformly doped bulk driven n-channel nano-MOSFET with 10-nm channel length. The source and drain regions are laterally identical with gradual doping characteristics. Special effects were considered to extract the realistic output of the device. Figure 2 represents the transfer characteristics of our test device.

3. ID Based Extraction Methods

These methods use the drain current (ID) directly in the extraction method of threshold voltage. Some common methods listed underneath are briefly discussed below.

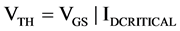

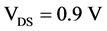

3.1. Constant Current Source (CCM) Method

This method determines VTH as the gate voltage for an arbitrary critical drain current (IDCRITICAL) value [16] [17] . To estimate the VTH using this method, ID versus VGS graph is plotted on a semi-logarithmic scale for two extreme values of VDS i.e. high biased and low biased. For our test device, we considered VDS = 0.9 V and VDS = 0.1 V respectively. The IDCRITICAL is technology reliant, generally considered as (0.1 μA) × (W/L), where W and L are the gate width and gate length.

(1)

(1)

IDCRITICAL referred in Equation (1) is designated such that VTH is on the transition point of linear-sub-threshold region of the device [11] [18] [19] .

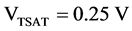

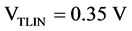

Implementation of CCM on Test Device

The technique was implemented on our test device square-sized NMOS with 10-nm technology node and was repeated in similar conditions on other sub 45-nm technology nodes. Figure 3 represents the simulated results and extraction output (VTLIN and VTSAT) using CCM on our test device.

Figure 2. Transfer characteristics of the test device for VDS = 0.1 V.

Figure 3. Extraction of VTSAT and VTLIN using CCM for VDS = 0.9 V and VDS = 0.1 V.

The outcome of the results was as follows:

@

@

@

@ .

.

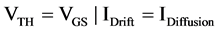

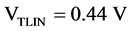

3.2. Drift-Diffusion Equality (DDE) Method

Diffusion current governs the total current in sub-threshold region whereas drift current dominates in strong inversion region. This DDEM process states that by applying low drain voltage (VDS ≈ 0.1 V), the threshold voltage is the distinctive gate voltage at which the condition IDRIFT = IDIFFUSION holds true [20] [21] . Hence, statistically we can represent the threshold voltage value as:

(2)

(2)

where IDrift and IDiffusion represent the drift current and diffusion current respectively.

Implementation of DDEM on Test Device

The technique was implemented on the test device.

The outcome of the result was as follows:

@

@ .

.

The DDEM process has the restriction of low biased VDS = 0.1 V. Since the device is always made to operate in linear region, hence the saturation region threshold voltage VTSAT could not be calculated. Figure 4 shows the simulated results of our test device for IDRIFT and IDIFFUSION with the variation in VGS to extract the threshold voltage.

4. Derivative of ID Based Methods

These methods use the derivative or the higher order derivate of the drain current value in the extraction method of threshold voltage. Fundamental VTH extraction methods using this respective technique are briefly discussed below.

Figure 4. Extraction of VTH using DDEM on the test device for VDS = 0.1 V.

4.1. Linear Extrapolation (LEM) Technique

In this LEM technique, we determine the VTH of the transistor using transconductance (gm) and IDS-VGS curve. The gm is defined as the derivative (slope) of ID-VGS relationship. The extreme gm obtained on the ID-VGS characteristic curve is used to extrapolate the gate voltage (VGS) as shown in Figure 5. The attained VGS is extracted VTH for the given conditions. The ID for linear region is associated with VGS as:

(3)

(3)

This LEM process provides clear steps for VTH assessment but it is partial to linear region of operation i.e. for low values of VDS. Maximum gm point is not obtainable for higher values of VDS. Furthermore, the DIBL effect also comes into picture for higher VDS and diminishes effective VTH values. Apart from these issues, this method also lacks to determine a constant VTH as dissimilar methods used for attaining maximum gm values. gm also depends on SCEs such as velocity saturation, overlap variations, extrinsic resistance, channel length modulation and so on. This reliance of gm and critical point of maximum gm is tough to accurately model. Henceforth, this produces loopholes in this process to precisely evaluate the VTH.

Implementation of LEM on Test Device

The technique was implemented on the test device.

The outcome of the result was as follows:

@

@ .

.

As described above, the Maximum gm is not obtainable for higher values of VDS. Hence special efforts were made to calculate VTSAT using this method. Figure 5 shows the transfer characteristics of the test device and the gm variation with the variation in VGS at constant VDS = 0.1 V.

Figure 5. Extraction of VTLIN using LEM for VDS = 0.1 V.

4.2. Quadratic Extrapolation (QEM) Method

Technique named Quadratic Extrapolation Method (QEM) is also called as “Linear Extrapolation in Saturation Region”. It is used to calculate threshold voltage using LEM in saturation region (VTSAT). As mentioned in LEM, the ID for linear region is proportional to (VGS − VTH). Similarly, ID in saturation region is proportional to (VGS − VTH)2 as shown in Equation (4):

(4)

(4)

Hence VTSAT can be extracted by extrapolating the curve  versus VGS at the inflexion point of the curve as shown in Figure 6.

versus VGS at the inflexion point of the curve as shown in Figure 6.

Implementation of QEM on Test Device

The technique was implemented on the test device.

The outcome of the result was as follows:

4.3. Second-Derivative (SD) Method

The second-derivative method (SDM), formerly entitled as transconductance change method [21] [22] , was developed to avoid dependence on series resistances. It evaluates VTH as the VGS value at which the derivative of the transconductance (i.e.,

The execution of this SDM process in the linear region is extremely sensitive to

Figure 6. Extraction of VTSAT using QEM for VDS = 0.9 V.

measurement error and noise, as the second derivative amounts to applying a high-pass filter to the measurement [23] .

Implementation of SDM on Test Device

The technique was implemented on the test device. The process was widely affected by noise. Special possessions of filtration and smoothening of curve were considered to extract the correct output as shown in Figure 8.

The outcome of the result was as follows:

4.4. Third-Derivative (TD) Method

In this TDM process, it has been proposed that the VTH can be extracted from the value

Figure 7. Extraction of VTLIN using SDM for VDS = 0.1 V.

Figure 8. Extraction of VTSAT using SDM for VDS = 0.9 V.

of VGS at which the third derivative of the current ID (i.e.,

Figure 9 and Figure 10 present the application of this TDM process to the 10-nm technology node test device in the linear and saturation regions, at drain voltages of 0.1 V and 0.9 V, respectively. It is clear from these figures that the TDM technique is extremely affected by tentative noisy data. Though investigational noise could be diminished by numerical flattening techniques or by fitting the semi-empiric models, the extracted VTH value would still be irreconcilable with that extracted by the SD method.

Implementation of TDM on Test Device

Figure 9. Extraction of VTLIN using TDM for VDS = 0.1 V.

Figure 10. Extraction of VTSAT using TDM for VDS = 0.9 V.

The technique was implemented on the test device. The method was vastly affected by the investigational noise. Hence it was challenging to extract the threshold values. Special properties of smoothening and filtration of the curve were considered to extract the correct output. Even after high considerations, it was observed that VTLIN value was lower than VTSAT value which is commonly unusual.

The outcome of the result was as follows:

4.5. Ghibaudo Method/Current-to-Square-Root-of-Transconductance Ratio (CsrTR) Method

The CsrTR method formerly called as Ghibaudo Method (GM) was developed to dodge the extracted VTH value dependence on mobility degradation and parasitic series resistance [25] [26] [27] . The ratio of the drain current to the square root of the transconductance, in the linear region, is given by Equation (5) as:

The GM technique, also occasionally called as ‘‘the modified Y function method’’, has been freshly enhanced for application to contemporary devices using a more universal mobility degradation model.

The VTH is extracted from the intercept of the GM versus VGS linear fit. Figure 11 shows the results of applying this method to the present test device in the linear region. As can be witnessed, it is not very clear in the method from where to linearly extrapolate to find the VGS axis intercept. It does not evidently show the supposedly expected linear behavior. Therefore, the linear extrapolation shown in Figure 11 is only a guess, amidst the evident non-linearity present.

Implementation of Ghibaudo Method (GM) on Test Device

The technique was implemented on the test device. Non-linearity in the curve caused difficulties in extrapolation process to estimate the required values. Figure 12 shows the results of applying this method to the present test device in the saturation region.

Figure 11. Extraction of VTLIN using Ghibaudo Method for VDS = 0.1 V.

The outcome of the result was as follows:

4.6. Transconductance to Current Ratio (TCR) Method

This method is based on calculating TCR as the ratio of transconductance to the drain current as described in Equation (6) [28] [29] :

It states that the threshold voltage can be determined as the value of VGS where TCR presents its maximum negative slope i.e. VGS corresponding to the minimum value of curve dTCR/dVGS. However, considering TCR by itself significantly increases random tentative noise, specifically in weak inversion.

Implementation of TCR Method on Test Device

The technique was implemented on the test device. The method was highly affected by the investigational noise as seen in Figure 13 and Figure 14 for extraction of VTLIN

Figure 12. Extraction of VTSAT using Ghibaudo method for VDS = 0.9 V.

Figure 13. Extraction of VTLIN using TCR for VDS = 0.1 V.

Figure 14. Extraction of VTSAT using TCR for VDS = 0.9 V.

and VTSAT respectively. Hence it was challenging to extract the threshold values. Filtration and smoothening of the curve like properties were applied to extract the correct output. Even after high considerations, it was observed that VTLIN value was lower than VTSAT value which is generally unusual.

The outcome of the result was as follows:

5. Integral of ID Based Methods

These methods use the integral of the drain current value in the extraction method of threshold voltage. Prevalent VTH extraction methods using this technique are briefly discussed below [30] [31] .

5.1. Transition Method

This TM technique was stimulated by the properties of the integral difference function D(V,I), which had been formerly defined for two-terminal device as [32] :

As shown in Equation (7), this function presents the advantageous features of eradicating the effect of any linear element (resistance) coupled in series with the device. To extract VTH, the drain current is constantly measured from below the expected value of VTH versus VGS with a small constant drain voltage (VDS ≈ 100 mV). Subsequently, the succeeding function TM is numerically calculated from the measured data:

where VG0 represents the lower limit of integration analogous to a gate voltage well below threshold in Equation (8). Usually chosen VG0 = 0. The logic of the method is based on the ideal case of a MOSFET, piecewise modelled as: ID = ILEAKAGE for VGS < VTH and ID is proportional to VGS for VGS > VTH. Using the previous streamlining supposition, we observe that:

1) Function TM presents a discontinuity at VTH;

2) TM = −VGS for VGS < VTH; and

3) TM = +VTH for VGS > VTH.

Since for a real device such simplifying conventions are apparently not precisely true, function TM will present an extreme value due to the mobility degradation and its value will be close to VTH.

A plot of TM versus VGS or ln(ID) should result in a straight line below threshold, where the current is dominated by diffusion and is principally exponential. As soon as VGS = VTH, the function TM should vitiate due to mobility degradation. The specified logic accords with the test device as shown in Figure 15. Hence the maximum of TM approaches the VTH value of the device. The shape of the curve is swayed by the parasitic resistance and mobility degradation effects, but not significantly its maxima, lest those effects are exceedingly prominent. Hence, the parasitic series resistance consequence is not totally eradicated since a MOSFET is not a two-terminal device with node current as ID and node voltage as VGS. Figure 16 represents the TM function output curve versus VGS to extract VTSAT for VDS = 0.9 V.

Implementation of TM Process on Test Device

The technique was implemented on the test device. Smooth curves were obtained. Hence it was easy to extract the threshold values. The VTLIN value and VTSAT value can also be extracted through the TM versus ID curve using the same procedure. On implementation of the mentioned logic, we got the same agreeing values of the threshold voltages.

The outcome of the result was as follows:

Figure 15. Extraction of VTLIN using TM for VDS = 0.1 V.

5.2. Normalized Mutual Integral Difference Method (NMID)

The NMID method was initially developed by He and co-workers in 2002 and it was also stimulated by the integral difference function NMID [31] , but in this case normalized by product IDVGS as shown in Equation (9):

Consequently, a plot of NMID versus VGS will characterize a maxima at VGS = VTH. Figure 17 exemplifies the claim of this method to the test device. Notice that the site of the maxima is autonomous of the constant term ‘‘1’’ which may be removed from Equation (11). A downside of this method is that the maximum of the curve is positioned in a wide region. Hence it becomes awkward to extract the analogous VGS value.

Implementation of NMID Process on Test Device

Figure 16. Extraction of VTSAT using TM for VDS = 0.9 V.

Figure 17. Extraction of VTLIN using NMID for VDS = 0.1 V.

The technique was implemented on the test device. Smooth curves were obtained. Flat curves of NMID to evaluate NMID max was challenging to extract the analogous threshold values. Figure 18 represents the NMID function output curve versus VGS to extract VTSAT for VDS = 0.9 V.

The outcome of the result was as follows:

5.3. Normalized Reciprocal H Function (NRH) Method

The NRH method can also be labelled as “Improved NMID Method”. Eliminating the ‘‘1’’ term and the factor ‘‘2’’ from NMID Equation (11), and considering that ID ≠ 0 at VGS = 0, yields a normalized version of the NRH function originally proposed in 2001 for extracting the threshold voltage of amorphous thin film MOSFETs, and later revised in 2010 to evaluate the sub-threshold slope of MOSFETs. Mathematically, the H function is represented as follows [33] [34] :

where ID0 is the drain current at VGS = 0. Limit of the integral can be considered as 0 to VGS in Equation (10). We propose that instead of using H(VGS) function, its reciprocal NRH(VGS) should be used to produce narrow maxima or minima:

A factor of 2 is added to the denominator in Equation (11) to allow a simple graphical explanation of its meaning. The numerator divided by 2 is the area of a triangle with a width of VGS and a height of ID − ID0. Then, NRH is the ratio of this triangle’s area divided by the area under the plot (the integral). Figure 19 and Figure 20 illustrate the application of this NRH method to the test device for the extraction of VTLIN and VTSAT respectively.

Figure 18. Extraction of VTSAT using NMID for VDS = 0.9 V.

Figure 19. Extraction of VTLIN using NRH for VDS = 0.1 V.

Figure 20. Extraction of VTSAT using NRH for VDS = 0.9 V.

Implementation of NRH Method on Test Device

The technique was implemented on the test device. Smooth curves were obtained. Flat curves of NRH to evaluate NRH max was challenging to extract the analogous threshold values.

The outcome of the result was as follows:

5.4. Reciprocal H Function (RH) Method

In view of TCR, the differential value of ID by itself expressively increases experimental noise, specifically in weak inversion, an analogous function for low gate bias. The plot of dRH/dVGS versus VGS exemplifies the above statement as it can be clearly seen in Figure 21 and Figure 22. The technique was proposed in 2010 based on the integration rather than differentiation to reduce unsolicited signal interference noise [33] [34] :

where RH is the reciprocal of function H predefined in NRH method; ID0 is the drain current flow at VGS = 0. Limits of the integral can be considered as 0 to VGS. It is anticipated that the RH function could also be used to extract the threshold voltage. The VTH can be extracted from the maximum negative gradient of the function RH i.e. VGS = VTH analogous to the minimum value of curve dRH/dVGS.

Implementation of RH Method on Test Device

The technique was implemented on the test device. The method was highly affected by the investigational noise. Hence it was challenging to extract the threshold values. As seen in Figure 22 and Figure 23, distinct features like smoothening and filtration of the curve were considered to extract the correct output.

The outcome of the result was as follows:

Figure 21. Extraction of VTLIN using RH for VDS = 0.1 V.

Figure 22. Extraction of VTSAT using RH for VDS = 0.9 V.

Figure 23. Implementation of HSPICE command on test device.

6. Self-Extraction Methods

These methods use the self-extracting techniques and circuits to extract the value of threshold voltage. Couple of methods under this category are briefly discussed below.

6.1. HSPICE Command Extraction Method

A substantially enhanced HSPICE feature that extracts MOSFET threshold voltage (VTH) based on the constant-current definition universally adopted by fabrication labs to measure, specify, and monitor VTH. Introduced in the 2009.09 release, HSPICE simulations compute constant-current VTH the exact same way VTH is measured in the fab [35] [36] .

For extracting VTH, the “.OPTION IVTH” command is available. This .OPTION IVTH feature is supported for Levels 54 (BSIM4), 69 (PSP100), and 70 (BSIMSOI4) MOSFET models along with latest PTM nano-MOSFET models. It shows acceptable results. This command extracts VTH using CCM and eliminates the use of IDCRITICAL. LX142 model accessible in HSPICE, presents the output results as VTH. Therefore, for short channel devices this process appears effectual in extracting VTH and also shows compatibility with the existing transistor models.

The HSPICE Command “.OPTION IVTH” was implemented on the test device. LX142 model accessible in HSPICE, presents the output results as VTH.

The outcome of the result was as follows:

6.2. Automatic Threshold Voltage Extractor Circuit (ATEC) Method

This proposed ATEC method implements the most popular industrial extraction algorithm (LEM) of biasing a saturated MOSFET to the linear portion of its

Few other similar ATEC designs with different implementation logics are also proposed to extract the VTH.

Implementation of ATEC Method on Test Device

The technique was implemented on the test device. The bulk driven 10 nm nano- NMOS model was used to simulate the circuit. The test device is made to work in linear region. Hence the outcome will be the threshold voltage in linear region (VTLIN). The transient analysis of the circuit gave the following results as shown in Figure 25.

Figure 24. Conceptual schematic of ATEC method.

7. Deviation Based Extraction Methods

Under this grouping, the VTH is extracted by determining either the deviation of the value or the difference between the measured values. Couple of methods using this logic are listed in this category and are briefly discussed below [39] .

7.1. Match-Point (MP) Method

Match-Point method was proposed in 1990 by B. El-Kareh and co-workers. This scheme subjectively evaluates VTH at the value of VGS at which the exponential subthreshold current semi-log extrapolation diverges by 5% from the measured ID.

This MP method exaggerates the weak inversion region neglecting strong inversion. Figure 26 and Figure 27 present the application of this method to the linear region

Figure 25. Extraction of VTH using ATEC for VDD = −VSS = 0.9 V.

Figure 26. Extraction of VTLIN using MP for VDS = 0.1 V.

Figure 27. Extraction of VTSAT using MP for VDS = 0.9 V.

and saturation region our test device producing an apparent VTH value VTLIN of 0.51 V and VTSAT of 0.52 V respectively. Of course, diverse values of VTH could be arbitrarily achieved by defining the deviation of the extrapolation at threshold at other values different from 5%. The shape of the semi-log curve may be swayed by the presence of parasitic resistance and other SCEs. This method is seldom used as it is more laborious and time consuming.

Implementation of MP Method on Test Device

The technique was implemented on the test device. Generally Match Point method is used to calculate threshold Values by plotting ID versus VGS curve with low biased drain terminal. Hence outcome is VTLIN. The results are extracted by using the semilog plot. We propose to calculate VTSAT by plotting

The outcome of the result was as follows:

7.2. Vin-Vout Difference (VVD) Method

In this VVD method, a new interpretation of the threshold voltage is presented as [40] :

The method is implemented by performing the transient analysis on the testing device. In other words, it states that VTH can be extracted by the voltage difference between the constant VG and VS at the normalized current in the ID-VS curves. As seen in Figure 28, the circuitry of VVD and the extraction method is straightforward and can be easily applicable in measurement apparatus [27] .

Implementation of VVD Method on Test Device

The technique was implemented on the test device. Figure 29 represents the transient

Figure 28. The proposed VVD circuit and the expected output to extract VTH.

Figure 29. Transient analysis of VVD for Vin = 0.9 V.

results of the VVD circuit. The circuit was compiled and simulated using SPICE. The circuit was analysed using predictive technology model (PTM) at 10-nm, 16-nm, 22-nm, 32-nm, and 45-nm technology node. The input gate voltage was set as 0.9 V. The Vdd was given as constant DC supply of 0.9 V. The multiple values of Load Capacitances (Cload) were used for the testing purpose, however, the VTH extraction results had negligible effect of the variations in the value. Transient analyses were performed on the compiled circuit to extract the threshold voltage value.

The outcome of the result was as follows:

The transient results gave the Vout value marginally equal to Vin, slightly a bit millivolts lower than Vin. Hence, as per the above mentioned logic of the referred extraction method, the calculated VTH is a very small value in millivolts which was not in accord with other extraction method outcomes. The extracted threshold voltage value also seems to be unrealistic. Hence we can accomplish that the VVD extraction method is considerably ineffective at nano-meter technology node.

8. Hybrid Extraction (HEM) Methods

Under this category, the HEM process uses multiple recognized schemes to extract VTH and combines the advantage of each. One of the hybrid extraction methods is explained below [34] .

This Hybrid extraction method overwhelms the constraints of above mentioned extraction techniques and compute VTH for all values of VDS. It syndicates both methods namely CCM and LEM mentioned beforehand to appropriately extract the VTH. Additionally, this method is also unaffected by the arbitrary value of IDCITICAL. For valuation of VTH using this method first the value of VTH for low biased VDS is attained using LEM (see Figure 30). Subsequently, IDCRITICAL is determined using CCM as mentioned above. Further, for higher value of VDS, VTH is defined as the gate voltage at ID for pre-calcu- lated IDCRITICAL value. However, the extracted value of VTH is not constant as the dependence of gm on other process parameters is not modelled accurately.

Implementation of Hybrid Extraction Method on Test Device

The HEM technique was implemented on the test device. VTLIN was calculated using LEM for ID versus VGS graph with low biased VDS, and correspondingly the IDCRITICAL was also evaluated. Furthermore, ID versus VGS graph is plotted with high biased VDS. Implementing the CCM technique on the plot by using the pre-calculated IDCRITICAL, we are able to calculate VTSAT. Hence we are able to extract VTLIN and VTSAT using Hybrid extraction method as seen in Figure 30.

The outcome of the result was as follows:

9. Compiled Simulation Results

All the predefined threshold voltage extraction methods were investigated and implemented at 10-nm Technology node and other sub 45-nm technology node. All the results are verified by extensive 2-D TCAD simulation and confirmed analytically. Various predictive technology models developed by the Nanoscale Integrations and Modelling (NIMO) Group at Arizona State University (ASU) were used to illustrate the characteristics of nano-MOSFETs. The models possess the competency to support short

Figure 30. Extraction of VTLIN and VTSAT using hybrid method for VDS = 0.1 V and VDS = 0.9 V.

channel effects, the gate leakage effects and various other second order effects to predict the realistic output. Table 1 presents a comparative result of largely applied threshold extraction methods for bulk driven nano-MOSFETs various sub 45-nm technology nodes. The VTH was analysed using predictive technology model (PTM) for bulk driven nano-mosfet at 10-nm, 16-nm, 22-nm, 32-nm and 45-nm technology node.

The results are tabulated in Table 1. Accuracy can be enhanced by considering more number of measured points.

10. Application of VTH Extraction Methods to Implement Noise Analysis

Noise analysis of the Resistive load Inverter were performed using various VTH extraction method values. Resistive load inverter is one of the most fundamental circuits of MOS family. It characterizes the basic operation of all static gates. With Load resistor (RL) in series with driver NMOS transistor, it has one input connected to the gate of NMOS and one output port connected to the drain terminal of the NMOS as shown in Figure 31. The Inverter Threshold Voltage VTH (inverter) is the value where output voltage is equal to input voltage.

Noise margin is the limit of noise that a circuit can endure without compromising the operation of circuit. It assures that logic “1” with finite noise added to it, is still recognized as logic “1” and not logic “0” and vice versa. It is principally the difference between

Table 1. VTH extraction using defined methods for different technology node.

signal and Noise value. Logically, the reference terms related Noise Margin analysis are described as below (Ref. Figure 32).

・ VOH: (Voltage Output High Value). VOH = Vdd because when the input voltage drops below VTH of the inverter, no current flows. No current flow in turn means no voltage drop across the load resistor and VOUT = Vdd = VOH.

・ VOL: (Voltage Output Low Value). If the input is driven to VOL = Vdd, then the driver NMOS transistor is “ON” and since (Vgs − Vt) > Vds, it is operating in linear mode. The VOUT will be at VOL and the VIN will be at VOH.

・ VIH: (Voltage Input High Value). When VIN = VIH, the output is at VOL and the NMOS is in the linear region.

・ VIL: (Voltage Input Low Value). To determine noise margin we need VIL which is one of two points where we have unity gain. When input low, output high and NMOS in saturation.

10.1. Introduction

Considering the output characteristics of a resistive load inverter; the threshold voltage of the NMOS (VTH) plays a significant role in determining the shape of the voltage transfer characteristic (VTC) of a resistive load inverter. The VTH appears as a critical parameter in expressions for VOL, VIL, and VIH. VOH is determined primarily by the power

Figure 31. General circuit diagram of resistive load inverter.

Figure 32. Representation of noise immunity and noise margins of resistive load inverter.

supply voltage Vdd. The adjustment of VOL receives primarily attention than VIL, VIH. Larger VTH results in smaller VOL resulting in larger transition slope and higher voltage swing as it can be perceived through Figure 33.

10.2. Noise Margin Analysis of Inverter for Diverse Values of Driver NMOS Threshold (VTH)

Ideally, when input voltage is logic “1”, the output voltage is expected to be at logic “0”. Hence, VIH is Vdd, and VOL is 0 V as shown in Figure 34. Alternatively, when input voltage is logic “0”, output voltage is supposed to be at logic “1”. Hence, VIL is 0 V, and VOH is Vdd. Using the values, the Noise Margins for an ideal inverter could be defined as follows:

・ NML (Noise Margin Low)

・ NMH (Noise Margin High)

Practically the situation is not identical. It is observed that due to number of secondary effects like voltage droop, ground bounce, internal resistances, practices, etc.; VOH is slightly less than Vdd i.e.

Figure 33. Typical VTC of a resistive load inverter.

Figure 34. VTC of an ideal resistive load inverter.

・ NML (Noise Margin Low)

・ NMH (Noise Margin High)

Hence, if input voltage (VIN) lies somewhere between VOL and VIL, it would be detected as logic “0”, and would result in an output which is acceptable. Similarly, if input voltage (VIN) lies between VIH and VOH, it would be detected as logic “1” and would result in an output which is acceptable.

10.3. Statistical Inference

Application of the extraction methods were implemented to calculate the Noise Immunity and Noise Margins for Resistive Load Inverter using 10-nm test device with Load Resistance RL = 100 Ω and Vdd = 1 V. Referring to Table 2, we can infer number of facts and properties that can be extracted from noise margin analysis regarding various threshold extraction methods.

・ We observe that with the increase in the Threshold voltage extraction value, the NMH decreases and NML increases. For an Ideal Inverter, Noise Margins should be equal. Using QEM method for VTH extraction, we obtain the most optimistic results (NMH ≈ NML) in this regards. (Ref. Figure 35 and Figure 36).

・ Using “.OPTION IVTH” command accessible in SPICE extraction method for VTH extraction, we obtain the maximum output voltage swing i.e. VOH − VOL for resistive load NMOS inverter (Ref. Figure 37).

・ In the well-designed inverter, the Threshold value of the circuit (Vin = Vout) is nearly equal to Vdd/2. We obtain the flawless results in this regards using CCM extraction method (Ref. Figure 38).

Table 2. Noise immunity and noise margins for resistive load inverter using 10-nm test device.

Figure 35. Noise margin variations vs. driver NMOS threshold values (VTH).

Figure 36. Plotting the |NMH-NML| vs. driver NMOS threshold voltage (VTH).

Figure 37. VTC of resistive load inverter vs. driver NMOS (VTH = 0.3 V) and RL = 100 Ω.

Figure 38. Inverter threshold VTH(Inverter) vs. driver NMOS threshold voltage (VTH).

・ The slope of the output curve within the transition region describes the propagation delay properties of the circuit. The variation in the VTH had a negligible effect on the slope of the curve resulting in nearly persistent switching characteristics for most of the extraction methods.

11. Conclusion

We presented, reviewed and critically compared several extraction methods currently used to determine the threshold voltage of bulk driven MOSFETs at 10-nm technology node and other various sub 45-nm technology nodes for precise evaluation of the respective method. The relative performance of all the methods was illustrated and compared under similar conditions by applying them to the test devices: bulk driven nano-MOSFETs with 10-nm technology node along with other various sub 45-nm technology nodes. We can perceive that the extracted threshold voltage largely depends on the method used for extraction specifically at nano-scale. The CCM has an ambiguous definition on the critical drain current (ID0) contingent on technology being used. The LEM, QEM and TM outcomes are affected by extrinsic resistance effects, mobility degradation, Short Channel Effects and other second order present effects. SD, TD, GM, RH and TCRM are also widely affected by noise and are also not based on ideal threshold voltage definition condition. The MP is seldom used as 5% deviation value gives an ambiguous definition of threshold. The VVD extraction method is considerably ineffective at nano-meter technology node. In NMID and NRH, the correct calculation of maxima in wide ranges makes the extraction task much more difficult. We can also infer number of facts and properties from noise margin analysis performed using various threshold extraction methods. QEM provides the most optimistic balanced noise margin results. The maximum output voltage swing was observed using SPICE extraction method. CCM delivers the most appropriate results in calculating Threshold value of the circuit. The above listed features and properties of various extraction methods can be helpful in merging the threshold voltage compact models at nano-level technology nodes.

Cite this paper

Swami, Y. and Rai, S. (2016) Comparative Methodical Assessment of Established MOSFET Threshold Voltage Extraction Methods at 10-nm Technology Node. Circuits and Systems, 7, 4248- 4279. http://dx.doi.org/10.4236/cs.2016.713349

References

- 1. Lundstrom, M. (1997) Elementary Scattering Theory of the Si MOSFET. IEEE Electron Device Letters, 18, 361-363.

https://doi.org/10.1109/55.596937 - 2. Liou, J.J., Ortiz-Conde, A. and García-Sánchez, F.J. (1998) Analysis and Design of MOSFETs: Modeling, Simulation and Parameter Extraction. Springer, New York.

https://doi.org/10.1007/978-1-4615-5415-8 - 3. Taur, Y., Wu, J.Z. and Min, J. (2016) A Short-Channel I-V Model for 2-D MOSFETs. IEEE Transactions on Electron Devices, 63, 1-6.

- 4. Tsividis, Y. (1999) Operation and Modelling of the MOS Transistor. Oxford University Press, New York.

- 5. Aoyama, K. (1995) A Method for Extracting the Threshold Voltage of MOSFETs Based on Current Components. Simulation of Semiconductor Devices & Processes, 6, 118-121.

https://doi.org/10.1007/978-3-7091-6619-2_28 - 6. Wong, H.S., White, M.H., Krutsick, T.J. and Booth, R.V. (1987) Modeling of Transconductance Degradation and Extraction of Threshold Voltage in Thin Oxide MOSFET’s. Solid-State Electronics, 30, 953.

https://doi.org/10.1016/0038-1101(87)90132-8 - 7. Subramanian, N., Ghibaudo, G. and Mouis, M. (2010) Parameter Extraction of Nano-Scale MOSFETs Using Modified Y Function Method. Proceedings of the European Solid-State Device Research Conference (ESSDERC), Seville, 14-16 September 2010, 309-312.

- 8. Turchetti, C. and Masetti, G. (1985) Analysis of the Depletion-Mode MOSFET Including Diffusion and Drift Currents. IEEE Transactions on Electron Devices, 32, 773-782.

https://doi.org/10.1109/T-ED.1985.22019 - 9. Ortiz-Conde, F.J., Garcia-Sanchez, J., Muci, A., Barrios, T., Liou, J.J. and Ho, C.-S. (2013) Revisiting MOSFET Threshold Voltage Extraction Methods. Microelectronics Reliability, 53, 90-104.

https://doi.org/10.1016/j.microrel.2012.09.015 - 10. Terada, K., Nishiyama, K. and Hatanaka, K.I. (2001) Comparison of MOSFET-Threshold Voltage Extraction Methods. Solid-State Electronics, 45, 35-40.

https://doi.org/10.1016/S0038-1101(00)00187-8 - 11. He, J., Xi, X., Chan, M., Cao, K., Hu, C., Li, Y., et al. (2002) Normalized Mutual Integral Difference Method to Extract Threshold Voltage of MOSFETs. IEEE Electron Device Letters, 23, 428-430.

https://doi.org/10.1109/LED.2002.1015230 - 12. Bazigos, A., Bucher, M., Assenmacher, J., Decker, S., Grabinski, W. and Papananos, Y. (2011) An Adjusted Constant-Current Method to Determine Saturated and Linear Mode Threshold Voltage of MOSFETs. IEEE Transactions on Electron Devices, 58, 3751-3758.

https://doi.org/10.1109/TED.2011.2164080 - 13. Katto, H. (1997) Device Parameter Extraction in the Linear Region of MOSFET’s. IEEE Transactions on Electron Devices, 18, 408-410.

https://doi.org/10.1109/55.622512 - 14. Tsuno, M., Suga, M., Tanaka, M., Shibahara, K., Miura-Mattausch, M. and Hirose, M. (1999) Physically-Based Threshold Voltage Determination for MOSFETs of All Gate Lengths. IEEE Transactions on Electron Devices, 46, 1429-1434.

https://doi.org/10.1109/16.772487 - 15. Zhou, X., Lim, K.Y. and Lim, D. (1999) A Simple and Unambiguous Definition of Threshold Voltage and Its Implications in Deep-Submicron MOS Device Modeling. IEEE Transactions on Electron Devices, 46, 807-809.

https://doi.org/10.1109/16.753720 - 16. Gildenblat, G., Li, X., Wu, W., Wang, H., Jha, A., Van Langevelde, R., et al. (2006) PSP: An Advanced Surface-Potential-Based MOSFET Model for Circuit Simulation. IEEE Transactions on Electron Devices, 53, 1979-1993.

https://doi.org/10.1109/TED.2005.881006 - 17. Miura-Mattausch, M., Feldmann, U., Rahm, A., Bollu, M. and Savignac, D. (1996) Unified Complete MOSFET Model for Analysis of Digital and Analog Circuits. IEEE Transactions on Computer-Aided Design, 15, 1-7.

https://doi.org/10.1109/43.486267 - 18. Rudenko, T., Kilchytska, V., Arshad, M.K.M., Raskin, J.-P., Nazarov, A. and Flandre, D. (2011) On the MOSFET Threshold Voltage Extraction by Transconductance and Transconductance-to-Current Ratio Change Methods: Part I-Effect of Gate Voltage-Dependent Mobility. IEEE Transactions on Electron Devices, 58, 4172-4179.

https://doi.org/10.1109/TED.2011.2168226 - 19. García-Sánchez, F.J., Ortiz-Conde, A., Mercato, G.D., Salcedo, J.A., Liou, J.J. and Yue, Y. (2000) New Simple Procedure to Determine the Threshold Voltage of MOSFETs. Solid-State Electronics, 44, 673-675.

https://doi.org/10.1016/S0038-1101(99)00254-3 - 20. Corsi, F., Marzocca, C. and Portacci, G.V. (1993) New Experimental Technique for Fast and Accurate MOSFET Threshold Extraction. Electronics Letters, 29, 1358-1360.

https://doi.org/10.1049/el:19930910 - 21. Brews, J.R. (1978) A Charge-Sheet Model of the MOSFET. Solid-State Electronics, 21, 345- 355.

https://doi.org/10.1016/0038-1101(78)90264-2 - 22. Huang, S.-Z. and Tai, Y.-H. (2005) A New Evaluation Method of the Threshold Voltage for a Low Temperature Poly-Silicon Thin Film Transistor in a Source Follower Configuration. IDMC, 442-444.

- 23. Loke, A., Wu, Z.-Y., Moallemi, R., Cabler, D., Lackey, C., Wee, T.T. and Doyle, B. (2010) Constant-Current Threshold Voltage Extraction in HSPICE for Nanoscale CMOS Analog Design. Synopsys Users Group (SNUG), San Jose, Advanced Micro Devices, Inc.

- 24. Zhou, X., Lim, K.Y. and Qian, W. (2001) Threshold Voltage Definition and Extraction for Deepsubmicron MOSFETs. Solid-State Electronics, 45, 507-510.

https://doi.org/10.1016/S0038-1101(01)00035-1 - 25. Jain, S. (1988) Measurement of Threshold Voltage and Channel Length of Submicron MOSFETs. IEEE Proceedings I (Circuits, Devices and Systems), 135, 162.

https://doi.org/10.1049/ip-i-1.1988.0029 - 26. Yan, Z.X. and Deen, M.J. (1991) Physically-Based Method for Measuring the Threshold Voltage of MOSFETs. IEEE Proceedings G (Circuits, Devices and Systems), 138, 351-357.

https://doi.org/10.1049/ip-g-2.1991.0060 - 27. Rudenko, T., Kilchytska, V., Arshad, M.K.M., Raskin, J.-P., Nazarov, A. and Flandre, D. (2011) On the MOSFET Threshold Voltage Extraction by Transconductance and Transconductance-to-Current Ratio Change Methods: Part II-Effect of Drain Voltage. IEEE Transactions on Electron Devices, 58, 4180-4188.

https://doi.org/10.1109/TED.2011.2168227 - 28. Lee, H.G., Oh, S.Y. and Fuller, G. (1982) A Simple and Accurate Method to Measure the Threshold Voltage of an Enhancement-Mode MOSFET. IEEE Transactions on Electron Devices, 29, 346-348.

https://doi.org/10.1109/T-ED.1982.20707 - 29. Yang, H. and Inokawa, H. (2012) A Differential Smoothing Technique for the Extraction of MOSFET Threshold Voltage Using Extrapolation in the Linear Region. Solid-State Electronics, 76, 5-7.

https://doi.org/10.1016/j.sse.2012.05.065 - 30. Tan, C., Xu, M. and Wang, Z. (2000) Proportional Difference Operator Method and Its Application in Studying Subthreshold Behavior of MOSFETs. Solid-State Electronics, 44, 1059-1067.

https://doi.org/10.1016/S0038-1101(99)00318-4 - 31. Picos, R., Roca, M., í?iguez, B. and García-Moreno, E. (2003) A New Procedure to Extract the Threshold Voltage of MOSFETs Using Noise-Reduction Techniques. Solid-State Electronics, 47, 1953-1958.

https://doi.org/10.1016/S0038-1101(03)00252-1 - 32. Dwivedi, A.K., Tyagi, S. and Islam, A. (2015) Threshold Voltage Extraction and Its Reliance on Device Parameters at 16-nm Process Technology. IEEE Conf (C3IT) 978-1-4799-4445- 3/15.

- 33. Berkeley Predictive Technology Model, UC Berkeley Device Group.

http://ptm.asu.edu/ - 34. Colalongo, L., Valdinoci, M. and Rudan, M. (1999) A Physically-Based Analytical Model for a-Si Devices Including Drift and Diffusion Currents. International Conference on Simulation of Semiconductor Processes and Devices, Kyoto, 6-8 September 1999, 179-182.

https://doi.org/10.1109/sispad.1999.799290 - 35. Thomas, F. and Holman, W.T. (2000) MOSFET Threshold Voltage Extractor Circuits Based on Square-Law Behavior. IEEE 42nd Midwest Symposium on Circuits and Systems, 2, 1118-1121.

https://doi.org/10.1109/mwscas.1999.867833 - 36. Tsuji, K., Terada, K., Takeda, R., Tsunomura, T. and Mogami, N. (2012) Threshold Voltage Variation Extracted from MOSFET C-V Curves by Charge-Based Capacitance Measurement. IEEE International Conference on Microelectronic Test Structures, San Diego, 19-22 March 2012, 82-86.

- 37. Lau, M.M., Chiang, C.Y.T., Yeow, Y.T. and Yao, Z.Q. (2001) A New Method of Threshold Voltage Extraction via MOSFET Gate-to-Substrate Capacitance Measurement. IEEE Transactions on Electron Devices, 48, 1742-1744.

https://doi.org/10.1109/16.936698 - 38. Dobrescu, L., Petrov, M., Dobrescu, D. and Ravariu, C. (2000) Threshold Voltage Extraction Methods for MOS Transistors. Proceedings of International Semiconductor Conference, Sinaia, 10-14 October 2000, 371-374.

https://doi.org/10.1109/smicnd.2000.890257 - 39. Ghibaudo, G. (1988) New Method for the Extraction of MOSFET Parameters. Electronics Letters, 24, 543-545.

https://doi.org/10.1049/el:19880369 - 40. Ortiz-Conde, A., García Sánchez, F.J. and Salazar, R. (2008) On Integration-Based Methods for MOSFET Model Parameter Extraction. 9th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Beijing, 20-23 October 2008, 428-431.