Circuits and Systems

Vol.07 No.10(2016), Article ID:70091,10 pages

10.4236/cs.2016.710282

Capacitor Pattern H-Bridge Multilevel Inverter (CPHMLI) Using Phase Diposition Pulse Width Modulation for Grid Applications

M. S. Saravanan1*, R. Jeyabharath2

1Department of ECE, Mahendra College of Engineering, Salem, India

2Department of EEE, KSR Institute for Engineering and Technology, Tiruchengode, India

Copyright © 2016 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Received 3 May 2016; accepted 15 May 2016; published 25 August 2016

ABSTRACT

This work presents an implementation of an innovative single phase multilevel inverter using capacitors with reduced switches. The proposed Capacitor pattern H-bridge Multilevel Inverter (CPHMLI) topology consists of a proper number of Capacitor connected with switches and power sources. The advanced switching control supplied by Pulse Width Modulation (PDPWM) to attain mixed staircase switching state. The charging and discharging mode are achieved by calculating the voltage error at the load. Furthermore, to accomplish the higher voltage levels at the output with less number of semiconductors switches and simple commutation designed using CPHMLI topology. To prove the performance and effectiveness of the proposed approach, a set of experiments performed under various load conditions using MATLAB tool.

Keywords:

Switched Capacitor Multilevel Inverter, Phase Diposition Pulse Width Modulation, Capacitor Pattern Based Multilevel Inverter, Total Harmonic Distortion, Cascaded H-Bridge, 17-Level Inverter

1. Introduction

In recent years, the amount of power equipment is increasing rapidly. Nowadays, multilevel converters have been increasingly used in high-power medium-voltage drive applications. Multilevel Inverter (MLI) has a distinctive arrangement that allows reaching high voltage and power levels without the use of transformers. They are specially suited for applications like renewable energy systems, electric vehicles (EVs) and other innovative power electronic utilities in medium and high power applications which need low THD. There are three types of multilevel inverters: diode clamped, flying capacitors, and cascaded H-bridge multilevel inverter which are mainly based on symmetric and asymmetric value of dc power supplies. Although each topology has its own advantages, drawbacks of each topology limit their applications. Although these converters have a lot of advantages over the classic inverters, using aforementioned conventional topologies needs more number of required power switches, power supplies and large capacitor banks. Furthermore voltage of the capacitors tends to be discharged theoretically and therefore charge balancing control processing is necessary.

Cascaded Multilevel Inverters (CMLI) are formed by the series connection of two or more single-phase H- bridge inverters. The multilevel converters which gained popularity in high power applications due to their low switch leg voltage stress and modularity. CMLI introduces the idea of using separate DC sources to produce an AC voltage waveform. Each H-bridge inverter is connected to its own DC source Vdc. By cascading the AC outputs of each H-bridge inverter, an AC voltage waveform is produced. The proposed converters can generate staircase voltage waveform at the output with high quality and desired spectrum. The desired output voltage is synthesized by appropriate switching of several dc voltage links which leads to decrease voltage stresses on switches and total harmonic distortion than previous multilevel converters.

2. Previous Research

Numerous related research works are already existed in literature which based on multilevel converter of the system. Some of them are reviewed here.

The conventional types of MLI configurations using reviews are discussed. The multilevel inverters are categorized into diode clamped (DCMLI) [1] , flying capacitors (FCMLI) and cascade H-bridge topologies (CHB) [2] . Many new topologies/source configurations are being proposed to serve high power applications [3] . A single-phase five-level topology for DC-AC conversion for distributed energy resources-based induction motor based grid applications. With a view to reduce power switch count, recently a new topology is introduced in [4] .

Although in [5] , the topology was extensively compared with the classical cascaded H-bridge (CHB) topology in terms of number of power switches, power rating of switches and switching losses, no mathematical formulations were presented. Further, a generalized structure of this topology is presented in [6] with mathematical formulations; still the treatment is restricted to symmetrical input DC sources only. It also presented comparative analysis against the CHB topology [7] based on number of power switches, number of switches conducting simultaneously and overall costs.

Nowadays, many researchers have presented numerous developed structures of MLIs with less number of key components such as number of required switches, gate drivers, power supplies and so on discussed [8] . Furthermore voltage of the capacitors tends to be discharged theoretically and therefore charge balancing control processing is necessary. The important schemes of a cascade boost switched-capacitors multilevel inverters (SCMLIs) in [9] .

The duty cycle of dc bus capacitors for FCMLIs by using the existing redundancy switching states (RSSs) [10] . A triplen harmonic compensatory method [11] based on fundamental switching strategy to extend the range of modulation index for three phase utility of 7-level CHB topology.

Level phase-shift modulation approach [12] to obviate the discharging problem in a capacitor-based 7-level CHB topology supplied by one dc voltage source for main unit and one floating capacitor for auxiliary unit. The switched-capacitors multilevel inverters (SCMLIs) contain several capacitors and switches which can connect dc power supply to ac output and are able to decrease the burden of power supply to achieve higher number of voltage levels [13] . Nevertheless, to attain the greater number of output voltage levels with less number of power semiconductors and simple commutation, a new type of SCMLIs have been emerged using the series/parallel switching strategy (SCISPC) [14] .

The distinctive features of these types of inverters are that they can increase the flexibility of systems by switching between several capacitors in series or parallel modes and therefore can transfer more input power to the output. A new family of cascade and hybrid SCISPC [15] topologies which have a modular structure and generate more output voltage levels with least of switches. But such structures have used the full H-bridge units with isolated dc voltage sources to change the polarity of output voltage waveform which makes more conducting loss through the current path components and increases the number of power switches.

The output voltage of a power inverter is to be a pure sinusoidal waveform with minimum distortion. But for the practical inverters, the output voltage is a series of rectangular waveforms. The major issues for the control of the power inverters are to get suitable modulation methods and to control the output rectangular waveforms to synthesize the desired waveforms. Therefore, a modulation control method is required to get a desired output voltage level and to eliminate higher order harmonics as much as possible. Hence the proposed method focussed on new cascaded H-bridge multilevel inverter topology with various modulation techniques has been discussed.

3. Proposed Capacitor Pattern H-Bridge Multilevel Inverter Topology (CPHMLI)

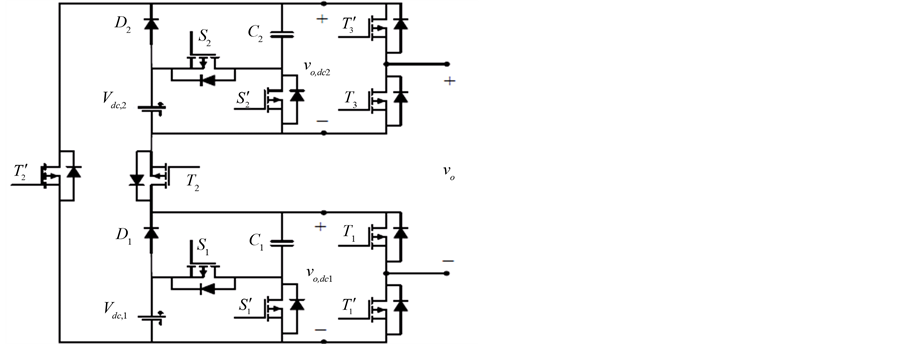

Figure 1 shows circuit topology of the proposed Capacitor pattern H-bridge Multilevel Inverter (CPHMLI). The circuit consists of two dc power supply, two capacitor, two passive power diode and eight active power switches. Photovoltaic (PV) cells and batteries can be used as a power supply in this structure. The Charging operations for capacitor C depend on Switches and which are connected in series and parallel arrangement. As it can be inspected, when the switch becomes ON, the capacitor C is charged to and when the switch turns off, the diode becomes reverse biased and capacitor is discharged. In this mode, the power supply energy and stored energy of C are transferred to the output.

Now by considering the proposed structure (Figure 1) shows the number of required switches, capacitor and diodes. From this structure the switches are triggered as complementary operation with each other’s and should not to be ON simultaneously. Also this structure can work on symmetric and asymmetric value of dc voltage sources. In symmetric structure, all of the dc sources are equal and that are different in asymmetric topology.

The Capacitor pattern H-bridge Multilevel Inverter (CPHMLI) based modulation algorithm proposed to remove the voltage oscillation for variable phase inverter circuits. The main aim is to reduce the number of switching commutations to have total control over the voltage swings. The amplitude of the low-frequency switching voltage oscillations increases under certain nonlinear loads. So that the situation causes the system becomes unstable due to voltage variations. The proposed topology based control strategies able to control the switching voltage oscillations than previous converters and n-level diode-clamped converters.

This work belongs to contribute the following features based on advanced modulation control strategy. The proposed inverter topology ultimately controls the voltage, thus removing the low-frequency switching voltage oscillations of multiphase converters under any unbalanced and nonlinear loads. The proposed PDPWM approach eliminates the sophisticated vector diagrams analysis with many vectors when the number of phases increases. Hence, the algorithm used as a recursive method that makes it extensible to n-phase converters in future. Additionally, it adds the new features of directly controlled closed-loop algorithm that does not involve any linear controllers.

4. Working Methodology

The controller monitors the level of input voltage Vin at each duty cycle and triggers one of the switch to flow

Figure 1. Proposed CPHMLI-Multilevel inverter structure.

the input voltage and this makes set of capacitors to be charged with the help of diode conduction state. By reading the input voltage Vin, the controller estimates the switching loss and choose the optimal circuit to be triggered based on the voltage value present in the capacitors present in the selected circuit. The controller maintains number of possible circuits as patterns and for each of the pattern the controller computes the possible output voltage Vout. Based on the output voltage could be generated a single switch is selected and the circuit is triggered to conduct the voltage and produce efficient output voltage.

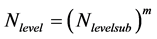

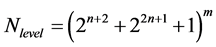

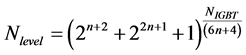

In this work, the number of required capacitors in each of proposed CPHMLI units is optimized from the view point of maximum produced output voltage levels for proposed CPHMLI with minimum number of IGBTs. This optimization is done based on asymmetric value of dc sources according to Equation (1). In general, the number of output voltage levels for proposed CPHMLI is obtained by:

(1)

(1)

where N Sublevels is the number of output voltage levels for proposed CPHMLI which is calculated by Equation (2). Then equation of (1) can be rewritten as:

(2)

(2)

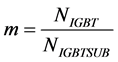

On the other hand, the relation of in terms of (number of required IGBTs for proposed CSMLI) and is equalized to Equation (2): NIGBT and m as

(3)

(3)

Also with inserting Equation (1) into Equation (3) and Equation (2):

(4)

(4)

In order to obtain the optimal number of capacitor from each of CPHMLIs, the variation of against for specific number of NIGBT.

Table 1 shows the possible operating modes based on charging and discharging states for both capacitors about 17 states. The charging states for both capacitors (states number of 5, 6, 8, 10, 12 and 13) and discharging states for one capacitor and charging states for another one or vice versa (other remaining states). In this Table 1, C and D refer to charging and discharging modes for capacitors, respectively. In order to generate more number of output voltage levels with optimum number of components, all of the capacitors should be charged by binary asymmetrical algorithm, according to this table. Also from this table it is obvious that, proposed topology is able to generate different positive output voltage levels by self-balancing ability.

In this case, all of the switches are driven by fundamental switching frequency whereas the sinusoidal reference voltage is compared with some available dc voltage levels and create the related gate switching pulses. The most advantage of this switching method is referred to low switching frequency which yields to reduction of switching loss. Details of fundamental switching modulation strategy are not objective of this paper.

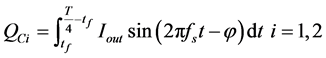

In addition from Table 1, it is clear that, to generate each of output voltage levels, only five switches are being involved in the current path. At this stage, to determine the capacitance of and, two assumptions are considered which one is related to output sinusoidal load current with phase difference between output voltage and current and the other is contribute to same duration in each step of staircase output voltage.

Thus, the maximum discharging amount of each capacitor can be defined as Equation (5) in one half cycles:

(5)

(5)

where, T is the period of one cycle, fs is the frequency of output voltage and I is the amplitude of load current, respectively. On the other hand, in proposed 17-level inverter, this time interval varies for Ts based on longest discharging cycle (LDC) of each capacitors. According to Table 1 the switching pulses are illustrated by Figure 2.

Thus, with considering the as maximum allowable voltage ripple, the optimum value of capacitors by

Figure 2. Output voltage waveform of 17-level inverter positive half cycle.

Table 1. Switching operation for CPHMLI topology.

5. Capacitor Pattern Based Pulse Generation

The proper duty cycle selected using capacitor pattern based pulse triggering for the proposed inverter topology. The pattern is generated based on the duty cycle according to the switch being triggered, the method identifies set of patterns which are triggered to get charged and set of capacitors gets discharged. The pattern generator identifies the capacitors at each pattern which gets charged at the specific selection of switch and their new voltage value will be updated to the pattern set.

6. Results and Discussion

The proposed capacitor pattern based hybrid multilevel inverter has been implemented and simulated using Matlab. The THD and efficiency of the proposed CPHMLI has been evaluated with number of duty cycles and has produced efficient Staircase output voltage.

Figure 3 shows the waveform generated using the mat lab simulation for output voltage, and it shows clearly that the output voltage has 17 level step output values. The graph has been generated by connecting the supply voltage with the CPHMLI circuit where the supply voltage is generated from renewable energy and stored in a battery.

Figure 4 shows the wave form of switching pulses for few step level which shows the various duty cycle of the proposed model. The graph has been generated by varying the duty cycle for each pattern of capacitor. The switches are connected in a H-bridge manner to get the proposer staircase AC output voltage. At the same time, The Diode and capacitance are connected parallel to the circuit which provides efficient output with increased voltage.

Figure 3. Simulation results for Proposed CPHMLI inverter for 17 level.

Figure 4. Switching pulses of the 17-level inverter using PDPWM scheme.

Topology Comparison

Table 2 shows the required component comparison between Cascaded multilevel inverter, cascaded H-bridge

multilevel inverter and proposed CPHMLI topology. The proposed topology requires very less number of IGBT switches, Diodes, capacitors and dc input voltage than the other methods. Therefore the proposed CPHMLI topology consists of ten switches, two diodes, two input dc voltage source and two capacitors to achieve 17 level step output voltage.

From the simulink environment FFT analyzer evaluates the different THD for various values of modulation Index ma. These evaluated values for different modulation techniques are listed in Table 3. From The measured values PDPWM produces very low harmonic distortion of 12.05% with respect to the modulation index of 1 for seventeen level step output voltages. Hence the proposed topology provides the low harmonics and higher efficiency for medium voltage high power applications. Table 3 shows the output line voltage THD obtained for the different level inverters at various values of ma for the three techniques.

From Graph 1, it is clear that the proposed CPHMLI inverter has Less Total harmonic distortion for various modulation index values such as M = 1, 0.8, 0.6, 0.4 than the others proposed earlier.

Table 4 shows the comparison of different multilevel inverter with proposed multilevel inverter using proposed controller system. The efficiency of the proposed model has been evaluated and tabulated.

Graph 2 shows that the proposed method has more efficiency compare to other two methodologies for 17-level cascaded H-bridge multilevel inverter topology and the same input values. Hence the proposed topology provides the low harmonics of 8.5% and higher efficiency of 95% for medium voltage high power applications.

7. Conclusion

This work proposed a novel schematic design and circuit for Capacitor pattern H-bridge Multilevel Inverter (CPHMLI) topology to reduce the distortions in output voltage. The proposed capacitor pattern based H-bridge Multilevel Inverter topology design in photovoltaic system was simulated with MATLAB/SIMULINK software. The proposed model reduces the required components and harmonic losses with the help of maintaining various

Graph 1. Performance comparison of THD for various Modulation index.

Table 2. Number of used Components between different inverter topology.

Table 3. Comparison of Modulation techniques (THD & Modulation index ma).

Table 4. Performance of various modulation technique based Inverter.

Graph 2. Comparison of different CHMLI system.

capacitor patterns which are discharged and list of capacitors which are gets charged at each duty cycle and at each switch condition. At each duty cycle the controller identifies the capacitors being charged and discharged according to the switch conditions. Also, the controller performs voltage approximation to identify the output voltage for each pattern. The proposed design reduces the voltage oscillations by adapting the capacitor as auxiliary circuit. The proposed schematic is hard wired to evaluate the performance and has produced efficient results. The proposed design has produced very good results and the output voltage and current produced are high. The efficiency produced by the design has been evaluated as 95% with low THD of 8.5% which is a successful output. The proposed design could be further improved by adapting more strategic voltage control algorithms and designs.

Cite this paper

M. S. Saravanan,R. Jeyabharath, (2016) Capacitor Pattern H-Bridge Multilevel Inverter (CPHMLI) Using Phase Diposition Pulse Width Modulation for Grid Applications. Circuits and Systems,07,3310-3319. doi: 10.4236/cs.2016.710282

References

- 1. Franquelo, L.G., Rodriguez, J.L., Leon, J., Kouro, S., Portillo, R. and Prats, M.A. (2008) The Age of Multilevel Converters Arrives. IEEE Industrial Electronics Magazine, 2, 1123-1127.

http://dx.doi.org/10.1109/MIE.2008.923519 - 2. Malinowski, M., Gopakumar, K., Rodriguez, J. and Pérez, M.A. (2010) A Survey on Cascaded Multilevel Inverters. IEEE Transactions on Industrial Electronics, 57, 2197-2206.

http://dx.doi.org/10.1109/TIE.2009.2030767 - 3. Rodriguez, J., Franquelo, L.G., Kouro, S., et al. (2009) Multilevel Converters: An Enabling Technology for High- Power Applications. Proceedings of the IEEE November, 1786-1817.

http://dx.doi.org/10.1109/jproc.2009.2030235 - 4. Renge, M.M. and Suryawanshi, H.M. (2008) Five-Level Diode Clamped Inverter to Eliminate Common Mode Voltage and Reduce dv/dt in Medium Voltage Rating Induction Motor Drives. IEEE Transactions on Power Electronics, 23, 1598-1607.

http://dx.doi.org/10.1109/TPEL.2008.925423 - 5. Liao, Y.H. and Lai, C.M. (2011) Newly-Constructed Simplified Single-Phase Multistring Multilevel Inverter Topology for Distributed Energy Resources. IEEE Transactions on Power Electronics, 26, 2386-2392.

http://dx.doi.org/10.1109/TPEL.2011.2157526 - 6. Ceglia, G., Guzman, V., Sanchez, C., Ibanez, F., Walter, J. and Gimenez, M.I. (2006) A New Simplified Multilevel Inverter Topology for DC-AC Conversion. IEEE Transactions on Power Electronics, 21, 1311-1319.

http://dx.doi.org/10.1109/TPEL.2006.880303 - 7. Zhong, D., Tolbert, L.M., Chiasson, J.N. and Ozpineci, B. (2006) A Cascade Multilevel Inverter Using a Single DC Source. Proceedings of the 21st Annual International Conference and Exposition of the IEEE Applied Power Electronics.

- 8. Wang, K., Li, Y., Zheng, Z. and Xu, L. (2013) Voltage Balancing and Fluctuation Suppression Methods of Floating Capacitors in a New Modular Multilevel Converter. IEEE Transactions on Industrial Electronics, 60, 1943-1954.

http://dx.doi.org/10.1109/TIE.2012.2201433 - 9. Yeung, Y.P.B., Cheng, K.W.E., Ho, S.L., Law, K.K. and Sutanto, D. (2004) Unified Analysis of Switched-Capacitor Resonant Converters. IEEE Transactions on Industrial Electronics, 51, 864-873.

http://dx.doi.org/10.1109/TIE.2004.831743 - 10. Du, Z., Tolbert, L.M., Ozpineci, B. and Chiasson, J.N. (2009) Fundamental Frequency Switching Strategies of a Seven-Level Hybrid Cascaded H-Bridge Multilevel Inverter. IEEE Transactions on Power Electronics, 24, 25-33.

http://dx.doi.org/10.1109/TPEL.2008.2006678 - 11. Gupta, K.K. and Jain, S. (2014) Comprehensive Review of a Recently Proposed Multilevel Inverter. IET Power Electronics, 7, 467-479.

http://dx.doi.org/10.1049/iet-pel.2012.0438 - 12. Angulo, M., Lezana, P., Kouro, S., Rodriguez, J. and Wu, B. (2007) Level-Shifted PWM for Cascaded Multilevel Inverters with Even Power Distribution. Proceedings of IEEE Power Electronics Specialists Conference, 2373-2378.

http://dx.doi.org/10.1109/PESC.2007.4342382 - 13. Hinago, Y. and Koizumi, H. (2012) A Switched-Capacitor Inverter Using Series/Parallel Conversion with Inductive Load. IEEE Transactions on Industrial Electronics, 59, 878-887.

http://dx.doi.org/10.1109/TIE.2011.2158768 - 14. Karami, B., Barzegarkhoo, R., Abrishamifar, A. and Samizadeh, M. (2015) A Switched-Capacitor Multilevel Inverter for High AC Power Systems with Reduced Ripple Loss Using SPWM Technique. Proceedings of 6th Annual International Conference of the Power Electronics and Technology Drive Systems (PEDSTC), 627-632.

http://dx.doi.org/10.1109/pedstc.2015.7093347 - 15. Liu, J., Cheng, K.W.E. and Ye, Y. (2014) Cascaded Multilevel Inverter Based on Switched-Capacitor for High-Fre- quency AC Power Distribution System. IEEE Transactions on Industrial Electronics, 22, 4219-4230.

http://dx.doi.org/10.1109/tpel.2013.2291514

NOTES

*Corresponding author.