Design and Implementation of Double Base Integer Encoder of Term Metrical to Direct Binary Code Application 371

operating frequency. So to implement an efficient sche-

me of piping, it is desirable to have some delays at all

stages [6].

Diagram of the encoder is shown in Figure 2 and de-

veloped in accordance with prudent use of a minimum

number of components, which reduces the space occu-

pied by the on-chip. MOSFETs-substrate transistors with

n-channel T1, T4 and T5 are connected to the negative rail

power supply Vss, and the substrate p-MOSFETs with

channel T2, T3 and T6 to the positive rail Vdd [7].

Encoder (Figure 2) consists of two CMOS—keys on

the basis of transistors T1, T2 and T5, T6, which are con-

trolled by the voltage at the input X1; Y0 determines the

MSB output binary code. Input X1 comes from the output

of the comparator switching threshold which corresponds

to the middle of the two-digit range input ADC. Keys at

the same switching voltage X0 and X2 from the outputs of

the other two comparators to generate low-order output

Y1 binary ADC. Based on the proposed scheme can be

implemented three-bit encoder, where a block with two-

digit designation DEC encoder according Proceeding si-

milarly, we obtain a four-digit encoder circuit based on

the three-digit encoder [8]. This requires the use of two-

input multiplexers labeled MUX, Figure 3 shows its’

scheme. Substrate MOSFET with n-channel T2, T4, T5,

T6, T8 and T10 are connected to the negative rail power

supply Vss, and the substrate MOSFETs p-channel T1, T3,

T7 and T9—to the positive rail Vdd. The multiplexer is a

signal at the address input A. When the signal at input A,

equal logical unit, the output signal from the input D1,

and when the signal A, equal to a logical zero, with input

D2. Inverters based on transistors T7 - T10 are the buffer

elements. Thus, increasing the bit similar to Figure 3.

Modeling was conducted with (tt, ss, ff, snfp, fnsp) for

three values of temperatures −40˚C and 27˚C, 85˚C. The

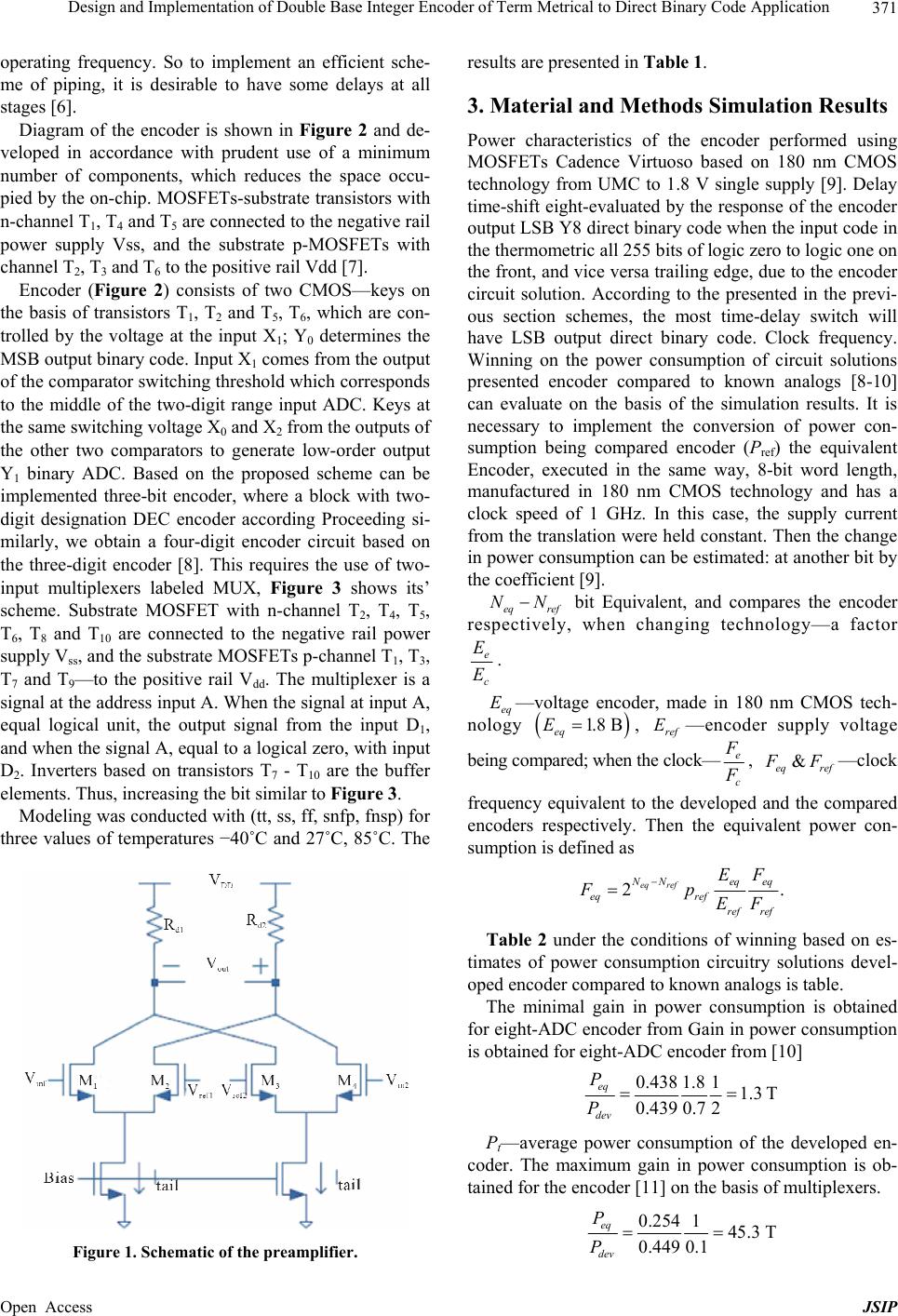

Figure 1. Schematic of the preamplifier.

results are presented in Table 1.

3. Material and Methods Simulation Results

Power characteristics of the encoder performed using

MOSFETs Cadence Virtuoso based on 180 nm CMOS

technology from UMC to 1.8 V single supply [9]. Delay

time-shift eight-evaluated by the response of the encoder

output LSB Y8 direct binary code when the input code in

the thermometric all 255 bits of logic zero to logic one on

the front, and vice versa trailing edge, due to the encoder

circuit solution. According to the presented in the previ-

ous section schemes, the most time-delay switch will

have LSB output direct binary code. Clock frequency.

Winning on the power consumption of circuit solutions

presented encoder compared to known analogs [8-10]

can evaluate on the basis of the simulation results. It is

necessary to implement the conversion of power con-

sumption being compared encoder (Pref) the equivalent

Encoder, executed in the same way, 8-bit word length,

manufactured in 180 nm CMOS technology and has a

clock speed of 1 GHz. In this case, the supply current

from the translation were held constant. Then the change

in power consumption can be estimated: at another bit by

the coefficient [9].

eqref bit Equivalent, and compares the encoder

respectively, when changing technology—a factor

NN

e

c

E

E.

eq —voltage encoder, made in 180 nm CMOS tech-

nology

E

1. 8 В

eq

E, —encoder supply voltage

ref

E

being compared; when the clock—e

c

, &

eq ref

F—clock

frequency equivalent to the developed and the compared

encoders respectively. Then the equivalent power con-

sumption is defined as

2.

eq ref

NN eq eq

eqref ref ref

EF

Fp

EF

Table 2 under the conditions of winning based on es-

timates of power consumption circuitry solutions devel-

oped encoder compared to known analogs is table.

The minimal gain in power consumption is obtained

for eight-ADC encoder from Gain in power consumption

is obtained for eight-ADC encoder from [10]

0.438 1.811.3 T

0.439 0.7 2

eq

dev

P

P

Pt—average power consumption of the developed en-

coder. The maximum gain in power consumption is ob-

tained for the encoder [11] on the basis of multiplexers.

0.254 145.3 T

0.449 0.1

eq

dev

P

P

Open Access JSIP